## Contents

| In       | Introduction 2 |        |                                                    |    |  |

|----------|----------------|--------|----------------------------------------------------|----|--|

| 1        | The            | Prob   | lem                                                | 9  |  |

|          | 1.1            | Event  | Building Overview                                  | 9  |  |

|          | 1.2            | Data   | Acquisition Strategies and Requirements            | 11 |  |

|          |                | 1.2.1  | Partial Event Building versus Full Event Building. | 13 |  |

|          |                | 1.2.2  | Data Flow Requirements                             | 14 |  |

|          |                | 1.2.3  | General requirements for trigger/DAQ               | 14 |  |

|          | 1.3            | Size o | f the Problem                                      | 16 |  |

| <b>2</b> | Eve            | nt Bu  | ilding                                             | 19 |  |

|          | 2.1            | Event  | Building and Interconnection Networks              | 19 |  |

|          |                | 2.1.1  | Time-Shared Bus Architectures                      | 20 |  |

|          |                | 2.1.2  | Multiple Bus Interconnection Network               | 21 |  |

|          |                | 2.1.3  | Multi-port Memory                                  | 22 |  |

|          |                | 2.1.4  | Crossbar and Other Switch-Based Interconnection    |    |  |

|          |                |        | Networks                                           | 23 |  |

|          |                | 2.1.5  | Integrated Processor Interconnection Network       | 25 |  |

|          | 2.2            | Event  | Building and Switching Technologies                | 26 |  |

|          |                | 2.2.1  | Circuit-switched Event Builders                    | 28 |  |

|          |                | 2.2.2  | Packet-switched Event Builders                     | 30 |  |

|          | 2.3            | Data   | Flow Options                                       | 32 |  |

|          | 2.4            |        | out Protocols                                      |    |  |

|          | 2.5            |        | em of Effective Throughput                         |    |  |

|          |                | 2.5.1  |                                                    |    |  |

ii *CONTENTS*

|   |     | 2.5.2  | Effective throughput of Network      | 38 |

|---|-----|--------|--------------------------------------|----|

| 3 | Tec | hnolog |                                      | 43 |

|   | 3.1 | _      | ·                                    | 43 |

|   |     | 3.1.1  | <u> </u>                             | 44 |

|   |     | 3.1.2  |                                      | 46 |

|   |     | 3.1.3  |                                      | 52 |

|   | 3.2 | Summ   | · ·                                  | 54 |

| 4 | Cas | e Stud | y: LHCb Event Building               | 57 |

|   | 4.1 |        | ·                                    | 58 |

|   |     | 4.1.1  |                                      | 59 |

|   |     | 4.1.2  | • •                                  | 62 |

|   |     | 4.1.3  | 36 /                                 | 63 |

|   | 4.2 | Netwo  | 9                                    | 63 |

|   | 4.3 |        |                                      | 65 |

|   |     | 4.3.1  |                                      | 66 |

|   |     | 4.3.2  |                                      | 66 |

|   |     | 4.3.3  | Meeting the Performance Requirements | 68 |

|   | 4.4 | Implei |                                      | 70 |

|   |     | 4.4.1  | Requirements                         | 70 |

|   |     | 4.4.2  |                                      | 71 |

|   |     | 4.4.3  | Meeting the performance requirements | 73 |

|   | 4.5 | Bound  | laries of This Work                  | 74 |

| 5 | Eve | nt Bui | ilding Protocol                      | 75 |

|   | 5.1 | Gener  | al Concepts                          | 75 |

|   |     | 5.1.1  | Sending an Event Fragment            | 76 |

|   |     | 5.1.2  | Receiving an Event Fragment          | 79 |

|   |     | 5.1.3  |                                      | 80 |

|   | 5.2 | Implei |                                      | 83 |

|   |     | 5.2.1  |                                      | 85 |

|   |     | 5.2.2  | No time-out                          | 87 |

|   |     | 5.2.3  |                                      | 89 |

|   |     | 5.2.4  |                                      | 95 |

CONTENTS iii

|   | 5.3 | Performance on a PC                    | 9 |

|---|-----|----------------------------------------|---|

| 6 | Em  | bedded Event Building 10               | 7 |

|   | 6.1 | What is an Embedded System?            | 7 |

|   |     | 6.1.1 History and future               |   |

|   |     | 6.1.2 Real-Time Systems                |   |

|   | 6.2 | Role of Embedded Processors            |   |

|   |     | 6.2.1 Video Game Player                |   |

|   |     | 6.2.2 Digital Watch                    |   |

|   |     | 6.2.3 Mars Explorer                    |   |

|   |     | 6.2.4 Conclusions                      |   |

|   | 6.3 | Embedded Event Building Justification  |   |

| 7 | A   | Gigabit Ethernet smart NIC: Tigon 2 11 | 9 |

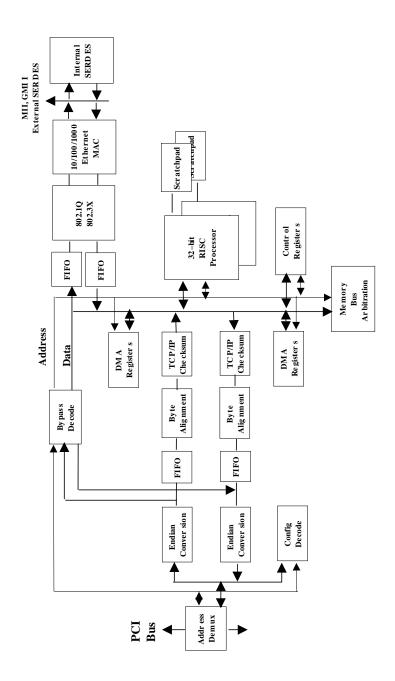

|   | 7.1 | Tigon 2: Architecture                  | 0 |

|   |     | 7.1.1 PCI Supported Features           |   |

|   |     | 7.1.2 Local Memory                     |   |

|   |     | 7.1.3 Internal Processors              |   |

|   |     | 7.1.4 Events                           | 4 |

|   |     | 7.1.5 Flash                            | 4 |

|   |     | 7.1.6 Mailboxes                        |   |

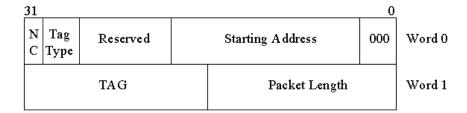

|   |     | 7.1.7 Ethernet Transmit Interface      |   |

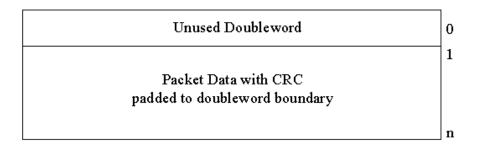

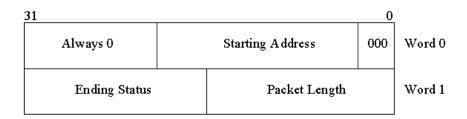

|   |     | 7.1.8 Ethernet Receive Interface       |   |

|   |     | 7.1.9 Gigabit Ethernet MAC             | 2 |

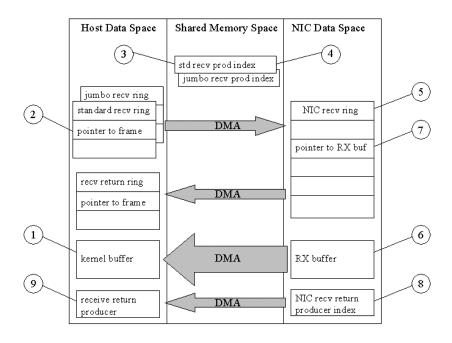

|   | 7.2 | Host/NIC Software Interface            | 3 |

|   |     | 7.2.1 Shared Rings                     | 5 |

|   |     | 7.2.2 Data rings                       | 6 |

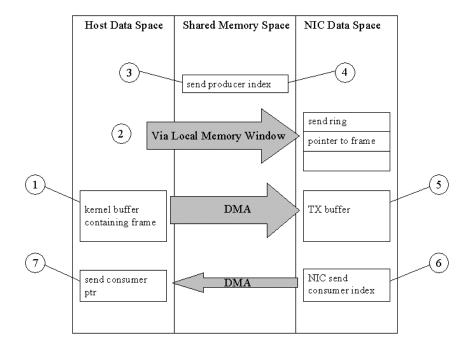

|   |     | 7.2.3 Transmit Flow Diagram            | 8 |

|   |     | 7.2.4 Receive Flow Diagram             | 0 |

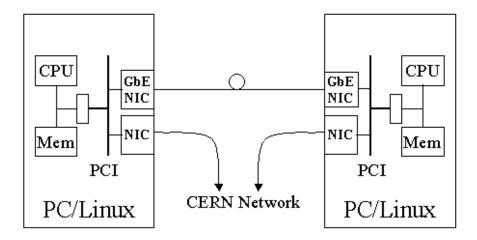

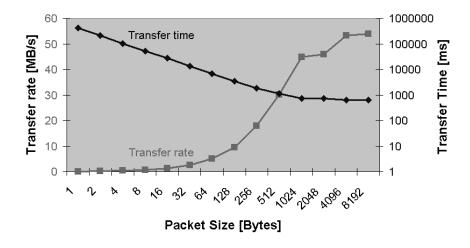

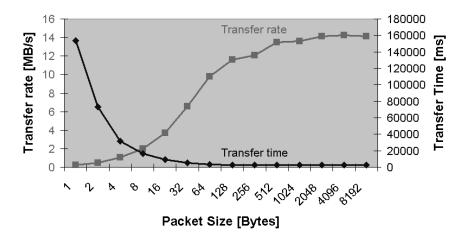

|   | 7.3 | NIC Performance Evaluation             | 1 |

| 8 | Eve | ent building on the NIC 14             | 9 |

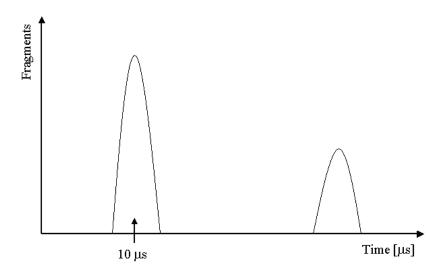

|   | 8.1 | Frequency of Fragments                 | 9 |

|   | 8.2 | Embedded Event Building Implementation | 2 |

|   |     | 8.2.1 Source Model                     |   |

iv CONTENTS

|        | 8.2.2 Destination Model                           | 156 |

|--------|---------------------------------------------------|-----|

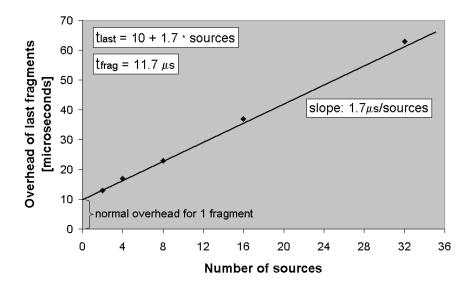

| 8.3    | Performance Results                               | 159 |

|        | 8.3.1 Comparison with Host to Host Event Building | 163 |

| 8.4    | Performance of Event Building                     | 165 |

| Conclu | sions                                             | 168 |

| Acknow | wledgements                                       | 174 |

## List of Figures

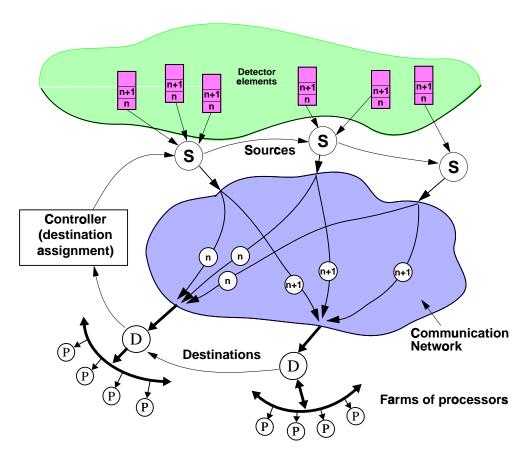

| 1.1  | Principle of event building                                    | 10  |

|------|----------------------------------------------------------------|-----|

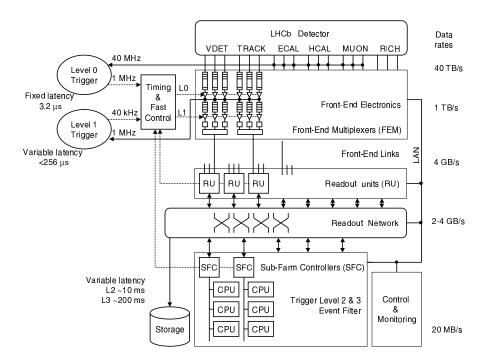

| 1.2  | General architecture of the trigger and data acquisition       | 1.0 |

|      | system for the LHCb experiment                                 | 13  |

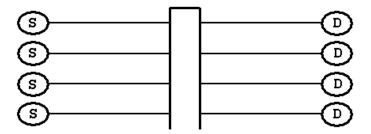

| 2.1  | Generic Interconnection Network                                | 20  |

| 2.2  | Shared Bus Interconnection Network                             | 21  |

| 2.3  | Multiple Bus Interconnection Network                           | 22  |

| 2.4  | Multi-port Memory Interconnection Network                      | 23  |

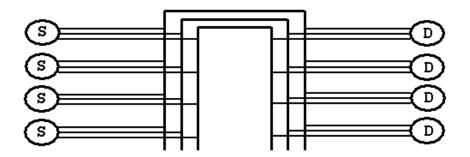

| 2.5  | Dual-Port Memory Interconnection Network                       | 24  |

| 2.6  | I/O Buffered Crossbar Interconnection Network                  | 25  |

| 2.7  | Mesh Interconnection Network                                   | 26  |

| 2.8  | Logical model of an event builder                              | 27  |

| 2.9  | A circuit switched "barrel shifter" event builder              | 29  |

| 2.10 | A packet switching event builder with permanent virtual        |     |

|      | connections fully interconnecting all sources and destinations | 31  |

| 2.11 | Connect overheads in connection switching                      | 32  |

| 2.12 | Technology overheads                                           | 37  |

| 2.13 | Software overheads                                             | 37  |

| 2.14 | Example of "packetisation" overheads                           | 38  |

| 2.15 | Bad solution between data submission and data preparation      | 39  |

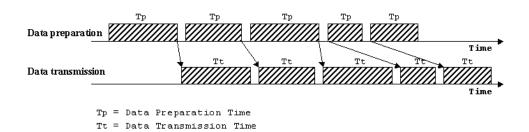

| 2.16 | Pipeline of data submission and data preparation               | 39  |

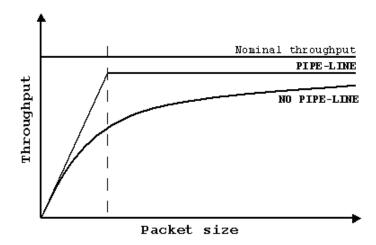

| 2.17 | Different throughput between pipe-lined and no pipe-line       |     |

|      | data submission and data preparation                           | 40  |

| 3.1  | An Ethernet Frame                                              | 47  |

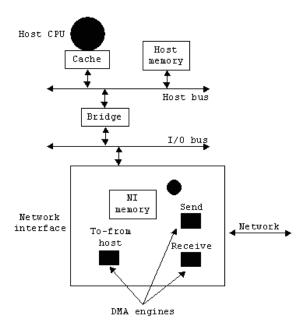

| 3.2  | Host and network interface architecture of Myrinet             | 53  |

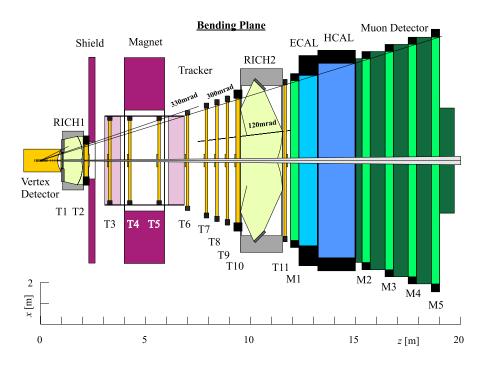

| 4.1  | The LHCb detector                                      |

|------|--------------------------------------------------------|

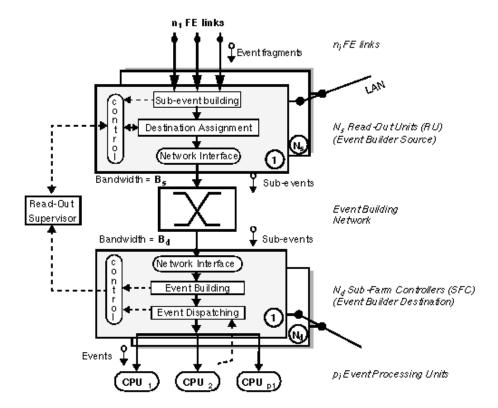

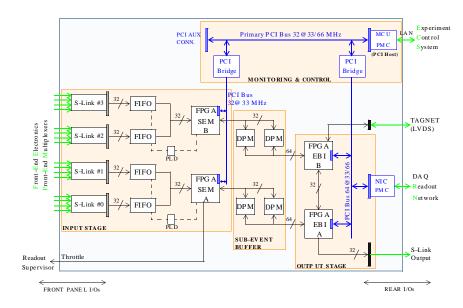

| 4.2  | Functional Model of the event builder 60               |

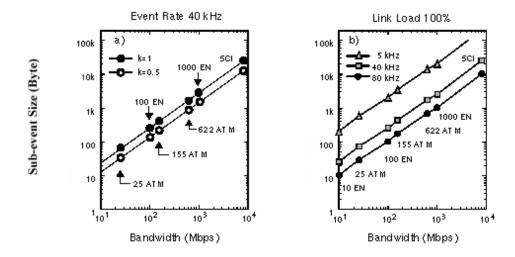

| 4.3  | Sub-event size versus link bandwidth 68                |

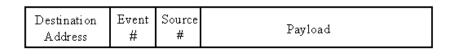

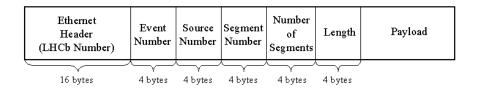

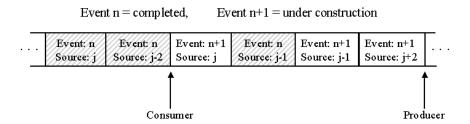

| 5.1  | Event Fragment PDU                                     |

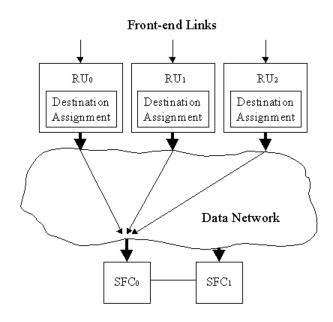

| 5.2  | Static destination assignment                          |

| 5.3  | Dynamic load balancing                                 |

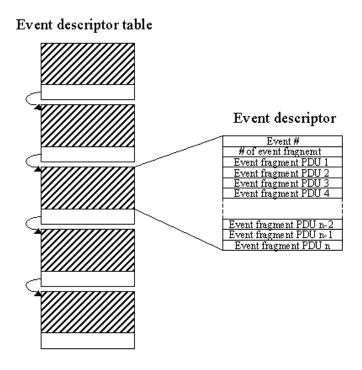

| 5.4  | Event descriptors                                      |

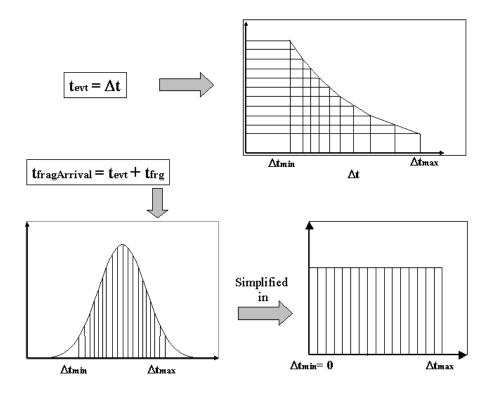

| 5.5  | Fragments generation                                   |

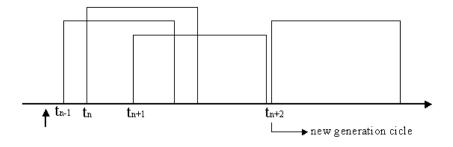

| 5.6  | Event generation                                       |

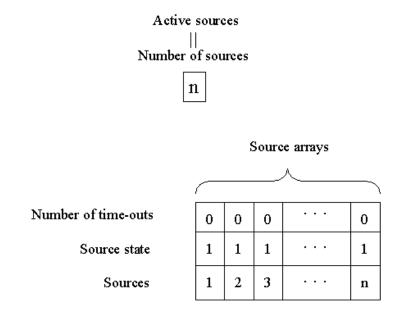

| 5.7  | Structure of the descriptor table                      |

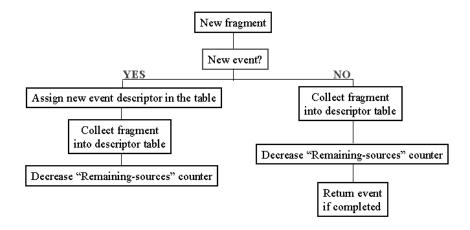

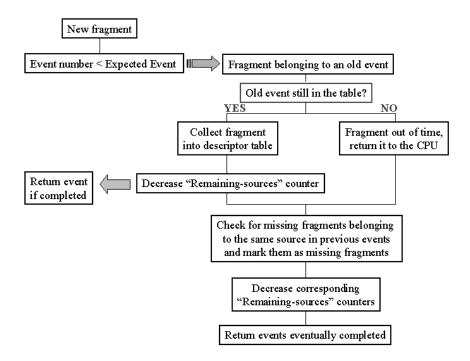

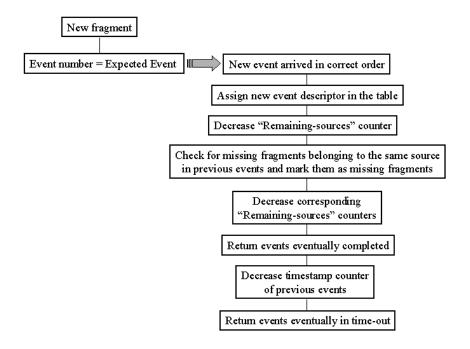

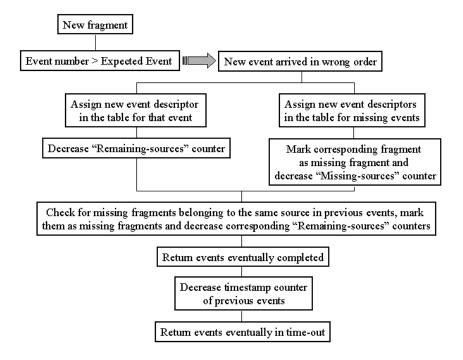

| 5.8  | No time out algorithm                                  |

| 5.9  | Structure of the descriptor table                      |

| 5.10 | Simple time-out: Case 1                                |

| 5.11 | Simple time-out: Case 2                                |

| 5.12 | Simple time-out: Case 3                                |

| 5.13 | Start up                                               |

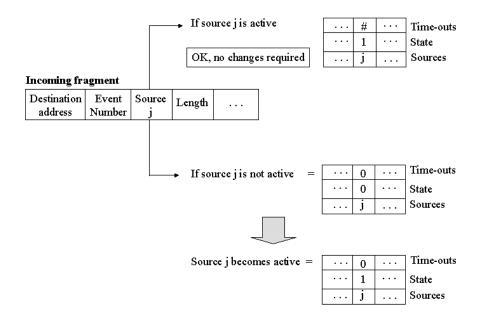

| 5.14 | New fragment                                           |

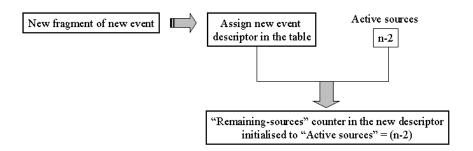

|      | Remaining sources counter updating when a new event    |

|      | fragment arrives                                       |

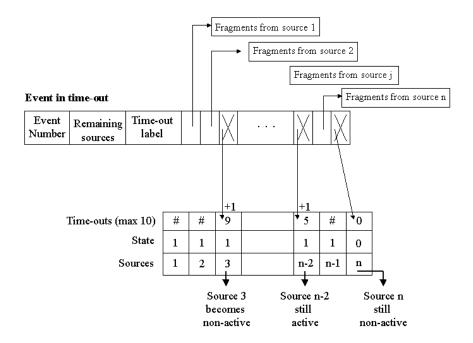

| 5.16 | Effects of events in time-out on source arrays         |

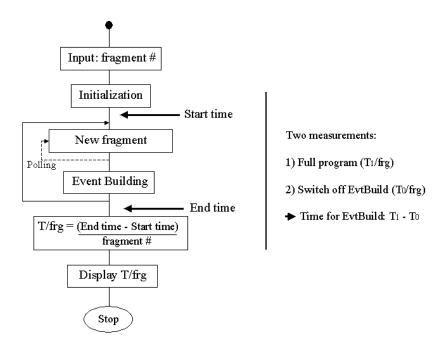

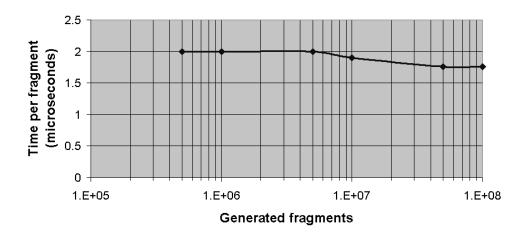

| 5.17 | Measurement of event building overhead 100             |

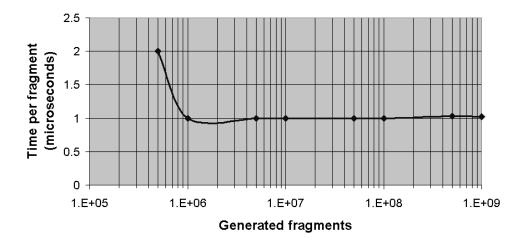

| 5.18 | Performance measurements of no time-out algorithm (in  |

|      | logarithmic scale)                                     |

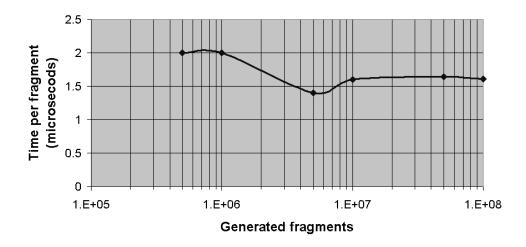

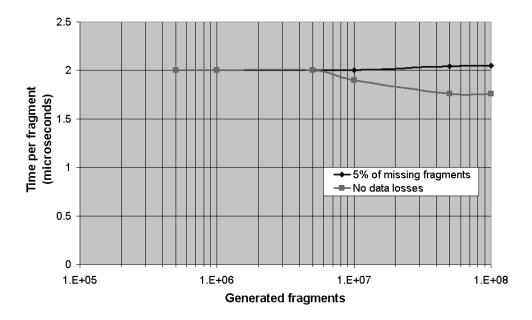

| 5.19 | Performance measurements of simple time-out algorithm  |

|      | (in logarithmic scale)                                 |

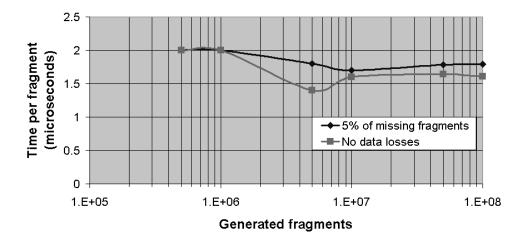

| 5.20 | Performance measurements of simple time-out algorithm  |

|      | (in logarithmic scale) with data losses                |

| 5.21 | Performance measurements of automatic adjustment algo- |

|      | rithm (in logarithmic scale)                           |

| 5.22 | Performance measurements of automatic adjustment algo- |

|      | rithm (in logarithmic scale), with data losses 105     |

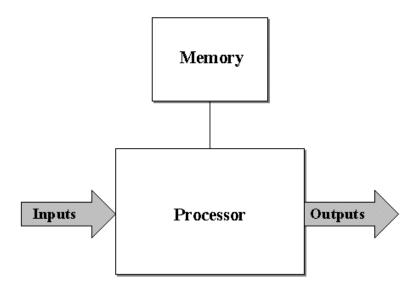

| 6.1  | Generic embedded system                                |

| 6.2  | Architecture of the RU model                           |

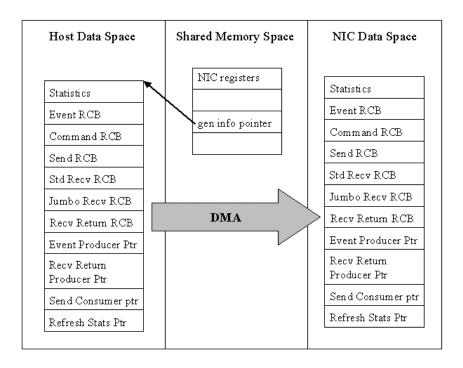

| 7.1  | Tigon 2 architecture                                                                                                                          |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| 7.2  | Ethernet transmit descriptor                                                                                                                  |

| 7.3  | Ethernet receive memory layout                                                                                                                |

| 7.4  | Ethernet receive descriptor                                                                                                                   |

| 7.5  | Memory model                                                                                                                                  |

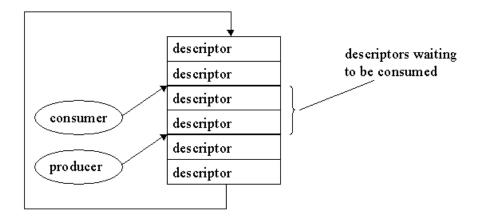

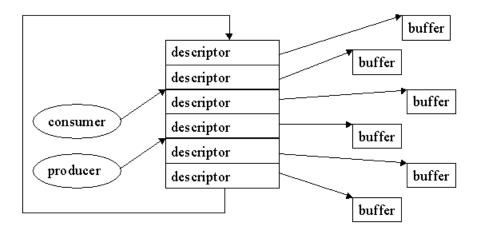

| 7.6  | Producer-consumer model                                                                                                                       |

| 7.7  | Producer-consumer model                                                                                                                       |

| 7.8  | Transmit Flow Diagram                                                                                                                         |

| 7.9  | Receive Flow Diagram                                                                                                                          |

| 7.10 | Test setup                                                                                                                                    |

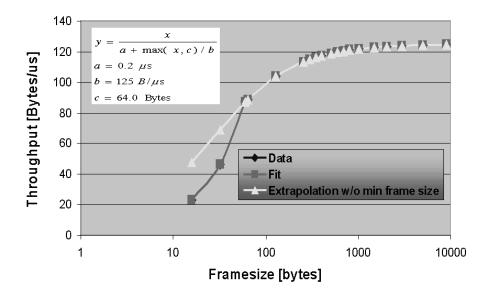

| 7.11 | UDP performance measurements                                                                                                                  |

| 7.12 | TCP performance measurements                                                                                                                  |

| 7.13 | Raw Ethernet performance measurements                                                                                                         |

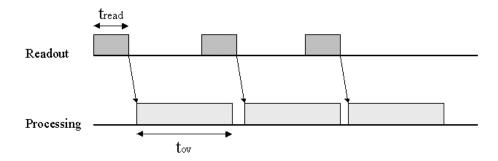

| 8.1  | Case 1: $t_{read} < t_{ov}$                                                                                                                   |

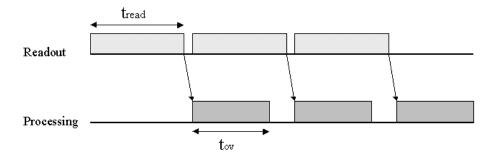

| 8.2  | Case 2: $t_{read} > t_{ov} \dots \dots$ |

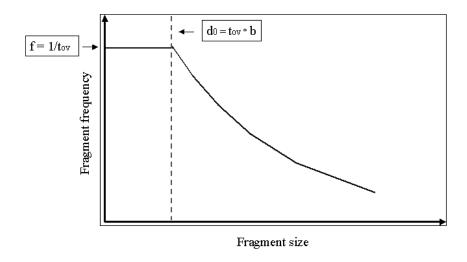

| 8.3  | Diagram of fragment frequency as function of fragment size 152                                                                                |

| 8.4  | Event fragment structure                                                                                                                      |

| 8.5  | Example of fragmented memory                                                                                                                  |

| 8.6  | Measurements of overhead per fragment                                                                                                         |

| 8.7  | Tested values for last event fragments                                                                                                        |

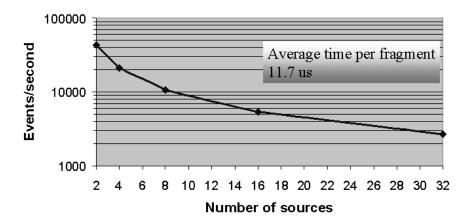

| 8.8  | Embedded event building performances, as function of num-                                                                                     |

|      | ber of sources (in logarithmic scale)                                                                                                         |

## List of Tables

| 1.1               | Trigger and data acquisition parameters of the four LHC experiments |

|-------------------|---------------------------------------------------------------------|

| 2.1               | Detector partitioning                                               |

| 3.1               | Network Technologies                                                |

| 4.1<br>4.2<br>4.3 | Detector partitioning                                               |

| 6.1               |                                                                     |

| 7.1<br>7.2        | Shared Configuration Block                                          |

## Abstract

In a high energy physics experiment, event building is the process of collecting data fragments, spread among many buffers, in order to reassemble the original event. Each assembled event is assigned to a processor in a large farm for on-line analysis.

The goal of the present work was to demonstrate the feasibility of implementing event building protocol in the processors embedded in the new generation of Network Interface Cards (NIC), in particular for Gigabit Ethernet technology. This implied the software implementation of the event building algorithms, their adaptation for their operation in the embedded processors, the development of a model of the event building conditions and the measurement and interpretation of performance of this solution. A comparison with the standard implementation on host processors provides the yardstick to judge the suitability of the proposed method.

This development was carried out within the team developing the Data Acquisition (DAQ) system for LHCb, one of the four experiments that have been approved for the future high energy collider LHC (Large Hadron Collider) at CERN.

The work requirements were to provide event building for a data acquisition system, which must sustain an input rate of 40 kHz, with some 100 data sources providing event fragments with a size of  $\sim 1$  kByte. The aggregate data acquisition rate is 4 GByte/s.

It has been demonstrated that event building on a Gigabit Ethernet smart NIC (the Tigon 2 Network Interface Card, by Alteon WebSystems) at a frequency of almost 100 kHz is sustainable for fragments with a size up to 1465 Bytes.

In the 20th century the need of gathering, processing and distributing information has become a dominant feature of our society.

"Among the other developments, we have seen the installation of worldwide telephone networks, the invention of radio and television, the birth and unprecedented growth of the computer industry, and the launching of communication satellites.

Because of the rapid technological progress, these areas are rapidly converging, and the differences between collecting, transporting, storing and processing information are quickly disappearing." [34]

Although the computer industry is young compared to the other industries, computers have made incredible progress in a very short time and they are now one of the leading system for handling information, besides telephones, televisions and radios.

The idea of the "computer centre" as a room with a large computer where users bring their work for processing has now totally disappeared. The old concept of a single computer serving all the needs of an organisation, like an university or a news agency, has also disappeared. It has been replaced by a model in which a large number of single-purpose computers, interconnected one to each other, works together and accomplishes jobs for many users.

These systems are called *computer networks* and they are one of the biggest challenges, in which the computer industry invests more. In few years we have migrated from small networks with a transfer power of few bits per second to wide area networks with gigabits transfer capabilities.

Due to this rapid and large development, networks have become quite common in many ordinary life aspects. Almost all business companies,

all universities, all researching activities have their network in order to share information inside the system and also outside, with the rest of the world. New buildings or transport systems (like trains) are built also with the network cabling prearrangement, beside the telephone cabling.

Nowadays, network capabilities can be used in many different fields but always with the same purposes: handling and moving around information.

Since few years, the possibility to take advantage of switching networks has been considered by the physics scientific community, in order to collect and store the data coming out from the physics experiments. New systems of data acquisition based on switching networks have been being studied. These are sort of "dedicated systems", because the initial requirements are usually very restricted and rigid, and the data rate is always high. Therefore, a data acquisition system must be perfectly studied, designed and developed, in order to be able to fulfil all the physics needs and to assure the experiments results.

The main topic of this work is to understand and explain what the event building really is, analysing its purposes, its general requirements and its typical solutions.

Then, a case of study will be proposed: the event building of the LHCb experiment. It will be analysed thoroughly in detail and the possibility to apply network capabilities to its requirements will be studied. Finally a data acquisition system, based on the new Gigabit Ethernet technology, will be proposed as a possible solution to the LHCb event building problem.

#### Working Environment

This work has been developed at CERN (European Laboratory for Particle Physics) [12], in Switzerland. The next future project of CERN is to build a new particle accelerator, the LHC (Large Hadron Collider) [13], which will start operating in 2005.

A collider is a machine which is designed to make bunches of particles circulate in opposite directions and to accelerate them until they achieve the desired energy. At this point, the trajectories of the two beams are

deflected by means of magnetic fields so that the particles collide. Surrounding the interaction points, experiments are built in order to detect the outcoming particles produced in the collision of the primary particles which the two beams consist of. The number of interesting physics interactions (signal events), which an experiment sees every second, is proportional to the so called luminosity of the accelerator. The luminosity L is defined by the following formula:

$$L = \frac{fkN^2}{4\pi\sigma_x\sigma_y}$$

where:

- f is the revolution frequency of the bunches

- $\bullet$  k is the number of bunches circulating in the machine

- N is the number of particles in each bunch

- $\sigma_x$  and  $\sigma_y$  are the transverse dimensions of the bunches

LHC is a circular accelerator which will take the place of LEP (Large Electron-Positron collider), inside the 27 Km underground tunnel in the Geneva area. It will bring protons into head-on collisions at the highest energies ever achieved; part of the LHC program will be dedicated to collide heavy nuclei. Inside LHC 2835 bunches of protons will circulate in each direction with an energy of 7 TeV, for a bunch crossing frequency of 40 MHz. Most of the 40 million interactions per second which will occur at LHC are not of interest from the physics point of view and they are referred to as background interactions. Therefore, each experiment, depending on its particular research field, will have to select among this big number the few thousands interesting events by means of a complex of hardware and software tools, called trigger. The data belonging to the events selected by the trigger are thus stored on tape for the physics analysis.

Four main experiments will exploit the LHC: the CMS experiment and the ATLAS experiment, mainly devoted to the research of the Higgs

boson, the ALICE experiment, which will study heavy nuclei interactions, and the LHCb experiment, whose physics motivation is shortly explained below.

#### Event Building and LHCb DAQ system

As previously mentioned, in high energy physics experiments, not all the collisions generate useful data for the analysis. Therefore, decision criteria must be immediately applied to the data at each collision time, in order to decide if either the produced event is an interesting one, from the physics point of view, and thus it has to be stored, or if it is an event which can be discarded, due to its lack of physics interest.

Because of the large amount of data and the high complexity of the decision criteria, the evaluation of an event is accomplished in several steps, or trigger levels. Depending on the experiment, one or two decision levels, based on simple topology and energy criteria, will be implemented in dedicated hardware logic, while one or more levels of software decisions are then applied to the remaining data for the final storage.

Only a small fraction of the total amount of data from each event is required for use in the initial decision. The rest of the data is scattered over many buffers and must be then collected in one place for the software analysis. The process of collecting the data fragments, spread among several buffers, into one destination, in order to reassemble the original physics event, is called *event building*.

LHCb [21] is the most recently approved of the four experiments which will run on the CERN's LHC accelerator. It is a special purpose experiment designed to study the CP violation <sup>1</sup> in the decay of b quarks. It has four levels of decision: Level-0 and Level-1, which are hardware driven, and Level-2 and Level-3, which are software decision level.

The role of the data acquisition (DAQ) system is to read data coming out from the Level-1 decision, to assemble complete events and to provide sufficient CPU power for the execution of the Level-2 and Level-3

<sup>&</sup>lt;sup>1</sup>CP violation was first discovered in neutral kaon decays in 1964. Its origin is still one of the outstanding mysteries of elementary particle physics. More details regarding the LHCb physics motivation can be found in [21], Chapter 1.

algorithms. The flow of data through the DAQ system is being studied using simulation data. The input rates are determined by the average event size, which is 100 kByte, and the Level-1 accept rate, nominally 40 kHz. This result in a total data acquisition rate of 4 GByte/s.

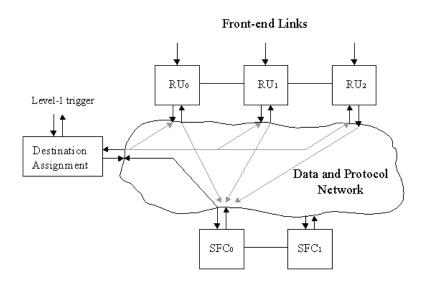

The current design contains the following functional components. The Readout Units (RUs) receive data from one or more Level-1 decision links and assemble the fragments belonging to each event into sub-events. Full event building is achieved by having all RUs dispatch their data into a readout network such that the fragment belonging to the same event arrive at the same destination. Complete events are assemble at the destination by a unit called the Sub-Farm Controller (SFC). This unit also has the role of allocating each event to one of the free CPUs it manages, and the Level-2 and Level-3 algorithms are executed on this CPU. Accepted events are written to storage devices.

#### Our Contribution

This work aims at studying and possibly realising a solution for the LHCb DAQ system, in order to manage the flow of data and to ensure events are assembled correctly. It is principally focused on the readout network and on its interfaces with the RUs (sources) and the SFCs (destinations). It is based on a *full-readout protocol*, where data are immediately routed through the readout network to the destinations as soon as they appear at the RUs.

This work will concentrate on a particular network technology: the new Gigabit Ethernet standard. In particular, we will work with a special Gigabit Ethernet Network Interface Card, which has an embedded processor inside. This choice is made in order to verify the possibility to develop a new data acquisition system in which the event building functionalities are executed inside the network interface. The final aim of the work is to study and realize this new embedded event building architecture and to verify that it is a feasible solution for the performance requirements of the LHCb DAQ system.

#### Structure of the Work

Before going into the detailed treatment of the argument, we summarise the work structure.

The first two chapters introduce the general concepts and requirements of the event building problem. The different strategies adopted in the past in order to face it are then described and some considerations on the applicability of switching network capabilities to the event building system are discussed.

In the following chapter, Chapter 3, the possible network technology competitors for the event building system are quickly described: ATM, Ethernet and Myrinet. More emphasis is given to the description of the Gigabit Ethernet standard, because it will be the baseline technology of the embedded event building project.

Chapter 4 introduces in all details the case of study of this work: the LHCb event building. The DAQ architecture and requirements are fully analysed, with the description of the RUs, the readout network and the SFCs and their corresponding roles and tasks. At the end of the chapter the boundaries and the scope of the work are specified.

In Chapter 5 there is the description of three different event building protocols developed and their overhead measurements are shown.

Chapter 6 and 7 are dedicated to the description of embedded systems, especially the one used for our purposes. The motivations for the embedded event building project are specified and the performance of the studied Gigabit Ethernet "smart" NIC are shown.

Finally, in Chapter 8, results are presented which show that embedded event building on a Gigabit Ethernet technology is feasible and fulfil the LHCb DAQ system requirements.

## Chapter 1

## The Problem

The demands on data acquisition systems for high-energy physics have been increasing at a rapid rate due to the higher luminosities and interaction rates. From the early days of high energy physics to some of present-day's experiments, when readout of a physics event is initiated, triggering on subsequent events is disabled until the readout is complete. Other factors in an experiment contribute to the experiment "dead-time" but readout is the dominating factor. The "dead-time", measured as a percentage, is approximately equal to the product between event readout time and trigger rate. Whenever possible it is held to less than 10%.

Now, with very high interaction rates and consequently very high trigger rates, readout time is an even larger fraction of the time between triggers. New techniques for physics event readout are now essential if we are to minimise dead-time. Several events worth of data must be buffered on or near the detector during triggering, such that when the readout is triggered the buffered data for that event may be readout quickly, without disabling the trigger (pipe-line).

### 1.1 Event Building Overview

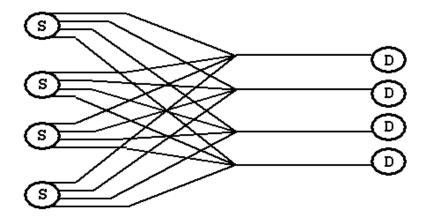

Only a small fraction of the total data from each event is required for use in the initial trigger decision. The remaining data is scattered over many front-end buffers and must be collected in one place for detailed analysis. An event builder is the device in a data acquisition system which provides a connection between the individual data sources (detector front-end electronics) and the data destinations (high-level event processors or online data storage). The process of collecting the data fragments coming from all sources into one destination is called *event building* (independently of whether or not the complete set of fragments is assembled). Figure 1.1 summarises the main principles of event building.

Figure 1.1: Principle of event building

Event builders have evolved in time from simple single channel 'funnels' through a minicomputer bus, to multiple parallel channels (each

with their own 'funnel' or characteristics) feeding arrays (farm) of processors. Regardless of the implementation, all event builders function as a data multiplexer. If data rates are low, this multiplexing operation can take place over a single time-shared bus using software controlled selection of source and destination. This is the technique used in the majority of data acquisition systems in the past. High-speed event builders were not necessary because the data rates which could be supported by the sources and destination were limited. This situation have changed in recent years. The ability to acquire, digitise and buffer data has increased and, similarly, the performance of high-level processors and the density of on-line data storage have been both improved. Unfortunately, the speeds of standard buses used for event building have not improved at the same rate and so the event builder has become the bottleneck in the data flow.

There are two possible solutions to this problem. Either the trigger efficiency can be increased, limiting data rates to the bandwidth of the event builder, or the event builder bandwidth can be increased. Techniques for improving trigger efficiency are dependent on the experiment. Techniques for improving event builder bandwidth can be considered independently.

# 1.2 Data Acquisition Strategies and Requirements

Nowadays the search for rare processes at the Large Hadron Collider <sup>1</sup> (LHC) experiments will require operation at very high luminosities. For example, for proton-proton collisions, the expected background interaction rate will be 10<sup>9</sup> Hz at the full luminosity at one collision point of

<sup>&</sup>lt;sup>1</sup>The Large Hadron Collider (LHC) is the new CERN accelerator which will start working in the year 2005. It will bring protons and ions into head-on collisions at higher energies than ever achieved before. This will allow scientists to penetrate still further into the structure of matter and recreate the conditions prevailing in the early universe, just after the "Big Bang" (more information about LHC can be found in [13]). Four big experiments will run on the LHC accelerator and they are: the ATLAS experiment, the ALICE experiment, the CMS experiment and the LHCb experiment.

the LHC. Bunch crossing occurring at a frequency of 40 MHz approximately, 25 interactions will occur per crossing. The average volume of zero-suppressed data associated with each bunch crossing (or event) is expected to be 1 MByte. Under these conditions a rejection factor from the trigger and data acquisition systems better than  $10^6$  is required in order to limit to reasonable volumes the data recorded on mass storage. To achieve the required rejection factors the experiments are adopting multi-level trigger strategies  $^2$ .

Depending on the experiment, one or two levels of trigger decisions (Level-1 or Level-0 plus Level-1), based on simple topology and energy flow criteria, will use coarse granularity data and will be implemented in dedicated hardwired logic. The fine granularity data from those bunch crossing that are accepted will be locally readout, formatted into event fragments and stored in readout buffers. The background rejection ratio will be further improved on-line by applying one or more levels of software triggers using the full-granularity data held in these readout buffers.

The required CPU power will be provided by a scalable farm of processors. Each successive event candidate is to be assigned to a different processor, which will access the distributed fragments of the assigned event and execute the filtering algorithms. A switching network will interconnect the readout buffers with the members of processor farm in order to allow the assembly of event fragments into (partial or complete) event records accessible by the processors.

Figure 1.2 [21] shows the complete architecture of the trigger and data acquisition system of the LHCb experiment and gives an idea about the dimensions of these complex kinds of apparatus.

$$T\left(egin{array}{c} Event data \& Apparatus \\ Physiscs channels \& Parameters \end{array}

ight) \Rightarrow egin{array}{c} REJECTED \\ ACCEPTED \end{array}$$

Since the detector data are not all promptly available and the function is highly complex, T(...) is evaluated by successive approximations called: TRIGGER LEVELS<sup>0,1,2,3</sup> (possibly with zero dead-time).

<sup>&</sup>lt;sup>2</sup>The trigger is a function of:

Figure 1.2: General architecture of the trigger and data acquisition system for the LHCb experiment

## 1.2.1 Partial Event Building versus Full Event Building

Very high (Level-0) Level-1 trigger rates and large event sizes can preclude the use of complete event data in the Level-2 triggers and force the choice of algorithms that operate on a subset of event data. This fact leads to what is called partial event building, which can be implemented in two different ways depending on the trigger strategy.

For example, the Level-1 trigger of CMS [16] is based on: a static subset of event data, the calorimeter and muon detectors, but does not use the tracker (which produces the largest part of event data). For the events accepted by the Level-2 trigger (at least an order of magnitude fewer than those that pass Level-1) the tracker data is then read

out and the more time-consuming and selective Level-3 algorithms are subsequently executed on the whole event data.

An other solution, implemented by the ATLAS experiment [22], consists in employing a dynamic partial event building strategy. In this architecture all detectors may contribute to the Level-2 trigger decision, but the algorithms are to be executed on subsets of event data guided by *Regions of Interest* (RoI) containing the physics *features* that caused the acceptance by the Level-1 trigger. The RoIs, which change for each event are located via pointers passed from the Level-1 trigger system. A sophisticated system is required to collect the data for the Level-2 trigger. Several solutions have been proposed regarding this topic and they can be found in [26] or in [22] (last review 31 March 2000, ch. 5 "DAQ/EF-1", pp. 27–56).

In the case of the LHCb experiment, a lower luminosity and the implementation of two levels of triggers (Level-0 and Level-1) on partial data allow to envisage to transfer all the data of accepted events to a processor executing the trigger of Level-2, taking advantage, in this way, of the standard full event building technique.

#### 1.2.2 Data Flow Requirements

Table 1.1 gives the design requirements for the triggers and the data acquisition for the four LHC experiments.

As we can see, the required aggregate bandwidth spans a wide range depending on the experiment target and the strategy adopted for the trigger. An estimated minimum aggregate throughput of 16 Gbit/s is required for the LHCb architecture, while at the other end of the spectrum a bandwidth of 600 Gib/s is required by the CMS architecture.

#### 1.2.3 General requirements for trigger/DAQ

General requirements for an event builder are:

• Event building rate and latency: In CMS experiment for example, the event building bandwidth is

| PARAMETER           | ALICE                   | ATLAS & CMS                  | LHCb                     |

|---------------------|-------------------------|------------------------------|--------------------------|

| Event size          | 40 MByte                | 1 MByte                      | 100 kByte                |

| Level-0 output rate | not applicable          | not applicable               | $1 \mathrm{\ MHz}$       |

| Level-1 output rate | $1~\mathrm{kHz}$        | $100~\mathrm{kHz}$           | 40  kHz                  |

| Level-2 output rate | $50  \mathrm{Hz}$       | 1–10 kHz                     | 5 kHz                    |

| Level-3 output rate | not applicable          | $100~\mathrm{Hz}$            | 200 Hz                   |

| Switching bandwidth | $30~\mathrm{Gbit/s}$    | $20$ – $600~\mathrm{Gbit/s}$ | 16-32  Gbit/s            |

| Data storage        | $10 \; \mathrm{Gbit/s}$ | $1~\mathrm{Gbit/s}$          | $160 \; \mathrm{Mbit/s}$ |

Table 1.1: Trigger and data acquisition parameters of the four LHC experiments

planned to be handled by a  $1000 \times 1000$  switch. Thus, each of the 1000 destinations must be capable of sustaining an average event building rate of  $\sim 100$  Hz for the Level-2 and at the same time  $\sim 10$  Hz for the Level-3.

#### • Achievable load factor:

In order to minimise the required hardware investment, the system design should be balanced such that, at maximum system throughput, the event builder aggregate bandwidth is used in a efficient way (>50%).

#### • Commercial products:

The use of commercially available components is preferred wherever possible in order to minimise development costs, to profit from lower prices due to high volume production and to ensure long-term maintenance.

#### • Open Standards:

In order to offer a good choice of suppliers and to ensure interoperability between components from different sources, the network technology should be open international standard that is widely adopted by industry.

#### • Technology life-cycle:

If possible, the life cycle of the chosen technology should match the one of the experiments, being sufficiently mature at the start of the experiments to ensure low prices, adequate performance and high reliability, and being still supported by industry at the end of the experiments (10–15 years later).

#### • Scaling:

The event builder architecture (hardware and software) must be scalable, so that it can be expanded (in dimensions and/or speed) without encountering bottlenecks that limit the growth in performance.

#### • Partitioning:

In order to support parallel development and testing of the different detector sub-systems, it must be possible to partition the event builder into a number of independent, concurrently running data acquisition systems.

#### • Operations and Management aspects:

Due to the large scale of the event builder it will be indispensable that the system incorporates features to ease its operation and management; for example, fault location, fault isolation, good monitoring and diagnostic tools, etc.

#### 1.3 Size of the Problem

In order to estimate the magnitude of the problem that an event builder must cover and solve, it can be useful to compare event building requirements with some other parameters, more common and understandable. For example, a comparison between event building needs and telephone traffic requirements could be helpful to realize the size of the problem.

If we focus in particular on the LHCb event building requirements (which are the real aim of this work), we can see that the requested aggregate switching bandwidth is at maximum 4 GByte/s. Because data will go only one-way, from readout sources to processor destinations, the event building protocol will use the network bandwidth only in one

direction but the network itself would be able to support, in principal, two-way traffic of 8 GByte/s.

Now telephone speech, when digitised, creates 64 kbit/s in each direction, or a total two-way digital traffic of 128 kbit/s. Thus, with an aggregate switching bandwidth of 4 GByte/s and a data traffic of 64 kbit/s, a maximum of 500.000 people can communicate by telephone in one direction and at the same time:

$$\frac{4 \times 10^9 \times 8 \ (bits)}{64 \times 10^3 \ (bits)} = 5 \times 10^5 = 500,000$$

Of course, telephone communications involve people from both sites of the line and so we can conclude that a switching bandwidth of 4 GByte/s would cover a telephone communication for 1 million people.

If we assume that during the day 20% of the whole population of a country is occupied in telephone communications at the same time<sup>3</sup>, our switching bandwidth of 4 GByte/s, that will be used for the LHCb data acquisition system, will cover the needs of 5 millions people, which are, for example, the needs of more or less the 10% of the whole Italian population.

<sup>&</sup>lt;sup>3</sup>This assumption could be overestimated, but we believe that 20% of a country population involved in telephone calls at the same time is not so far from reality, at least in some times of the day.

## Chapter 2

## **Event Building**

Event building is faced with a lot of problems which can meet different solutions, according to the available technologies and the physics needs claimed by each specific experiment. Big difficulties are related to the event traffic management: the choice of which connection solution between data generators and data analysers is the most suitable, the choice of which kind of system architecture and communication protocol are the right ones to obtain the best performance, are really hard and, at the same time, decisive choices. Much effort have been spent to propose new and different solutions and to better exploit the new emerging technologies.

This chapter deals with these topics and tries to explain all the distinct solutions considered in the past and nowadays, paying special attention to still unresolved problems.

# 2.1 Event Building and Interconnection Networks

Figure 2.1 shows a generic Interconnection Network (IN) used in multiprocessor and telecommunications systems. In high energy physics, the data source (S) is typically a detector subsystem and the destination (D) is a single or a farm of programmable processors. The IN and its associated control is referred to as an "event builder". Because the pattern of data flow is well defined (unidirectional and evenly distributed), a general-purpose IN can often be simplified for use as an event builder.

Figure 2.1: Generic Interconnection Network

Various kinds of techniques have been developed to improve the effects of using an IN on data acquisition systems and the following subsections give a brief overview about some of these historical architectures (further and in-depth information regarding this topic can be found in [9]).

#### 2.1.1 Time-Shared Bus Architectures

The shared bus, shown in figure 2.2, is the most common method of interconnecting multiple sources and destinations. Bus bandwidths of several tens of MBytes can be supported during block transfers, but the average data rate is usually much less due to the overhead of processor setup and bus access protocols.

A single shared bus has the advantage of simple control and low cost. It also provides bidirectional transfer capability for down-load and initialisation. With repeaters it can scale indefinitely, although the total bandwidth does not increase and will usually decrease. The main cost element is the need for high-speed interface circuitry, which must be designed to support the full transfer rate of the bus even if each module is connected for only a small fraction of the total readout time. Failure of

the bus itself will disable the entire system, but failure of an individual module is usually not critical.

Figure 2.2: Shared Bus Interconnection Network

In most cases, data readout is controlled entirely by the processor. A processor will arbitrate for the bus and then read event data from each of the front-end buffers before releasing the bus to the next ready processor. In more complicated system, an intermediate event builder will read the front-end buffers and then write data directly into the memory of a selected processor. In some architectures several independent busses may operate in a tree-like structure to reduce dead-time at the front-end. However, without intermediate data compression, the net bandwidth in a tree-structured system is always equal to that of a single bus.

#### 2.1.2 Multiple Bus Interconnection Network

Many standard bus specifications and multiprocessor implementations define a second or third bus (figure 2.3), which can operate in parallel with the main system bus. Additional bandwidth is gained only if processors do not contend for the same global resources. This approach is usually limited to one or two additional busses by the physical packaging constraints of standardised systems. A multiple bus architecture can be very reliable since failure of any single bus has no adverse effect other

than a reduction in total system bandwidth.

Figure 2.3: Multiple Bus Interconnection Network

With multiple busses, several events can be read out simultaneously. If events are assigned to specific buffers, then simple bus arbitration can be used to control readout sequences. Otherwise, a small amount of centralised control is necessary. As in any parallel system, the front-end buffers must be able to hold more than one complete event.

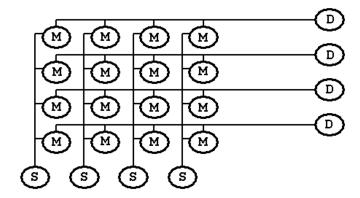

#### 2.1.3 Multi-port Memory

Both the data sources and the destinations in the multiple bus architecture are multi-ported, but the same bandwidth can be obtained with multiple ports on only one side of the interconnect as shown in figure 2.4. Reliability is reduced because there is only one path from a particular source to a particular destination. Arbitration is handled by the multiported module rather than the bus.

This approach is still limited by the number of physical ports which can be supported by a module.

To allow greater expansion, multi-port memories can be further subdivided into an array of independent dual-ported buffers as shown in figure 2.5

Figure 2.4: Multi-port Memory Interconnection Network

Dual-ported memory is easier to implement since it is available in the form of commercial integrated circuits (dual-ported static RAMs, FIFOs or video DRAMs).

With dual-ported memory, the limitation now becomes the total number of buffers required in a large system instead of the number of connections per buffer. The number of buffers can be reduced by using higher speed output busses, (allowing a rectangular instead of a square array) or possibly by implementing some kind of multistage memory architecture.

In the dual-ported memory architecture, the fragments of a given event are transmitted in parallel from the front-end subsystem to buffers in a selected row. These fragments are then readout sequentially by a processor while the next event is being transmitted to another row buffer.

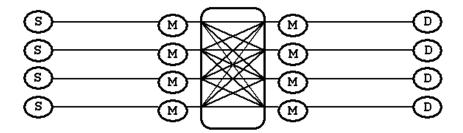

#### 2.1.4 Crossbar and Other Switch-Based Interconnection Networks

The dual-ported memory architecture in figure 2.5 is actually a form of buffered crossbar switch. A crossbar switch provides a complete,

Figure 2.5: Dual-Port Memory Interconnection Network

non-blocking<sup>1</sup> interconnection between all inputs and outputs. It is an ideal interconnection network in terms of bandwidth efficiency. Crossbar switches, used in packet-switching networks, can be classified by the location of buffering (input, output, embedded) with respect to the switching matrix. If the buffers are moved to the inputs or outputs (figure 2.6) the switching matrix itself can be confined to a very small area. As an added advantage, only 2N large dual-ported buffers are required if the buffers are positionated at the inputs and outputs, whereas  $N^2$  smaller buffers are required if they are embedded in the switching matrix. The total amount of memory required is the same regardless of where it is positioned, but as a practical matter it is easier and less expensive to implement a small number of large dual-ported buffers compared to a large number of small dual-ported buffers.

The full crossbar requires  $N^2$  crosspoints, which may be impractical for larger systems. For systems with twenty or more data channels, a

<sup>&</sup>lt;sup>1</sup>A network can be either *blocking* or *non-blocking*. Blocking occurs when information cannot be transmitted through the network due to the competition for the same internal or external data-path. When this feature can be avoided, the network is called non-blocking

multistage network can provide essentially the same non-blocking characteristics as the crossbar switch, using fewer crosspoints.

Figure 2.6: I/O Buffered Crossbar Interconnection Network

#### 2.1.5 Integrated Processor Interconnection Network

The mesh interconnection network (figure 2.7) is popular in the construction of large multiprocessor systems. These INs are formed by overlaying an array of processors on the dual-ported memory array of the buffered crossbar switch. Some cost reduction may be possible with this approach. The mesh also allows direct processor to processor communication, not normally a requirement in event building but potentially useful in the analysis of overlapping events or methods of event building which divide the analysis software into stages, where each stage resides in a different processor. Reliability can be higher for a mesh interconnect since there are multiple paths for each packet transfer. In practice though, the control complexity and possibility of message deadlock allows only orthogonal routing. Otherwise a packet may inadvertently be routed into a circular path and lost or delayed. Intelligent buffered routers are necessary for event builders applications because there is nearly continuous traffic on all links in the network. If the processor managed the inter-node communication directly, there would be little time left for processing the data.

Figure 2.7: Mesh Interconnection Network

# 2.2 Event Building and Switching Technologies

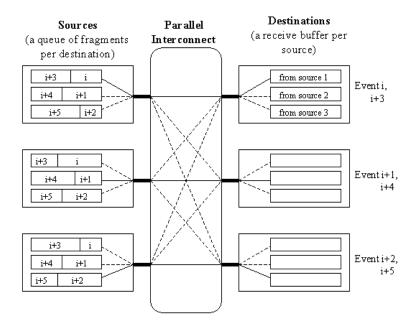

Figure 2.8 shows the logical model of  $3 \times 3$  event builder. By generalising the figure to a  $N \times N$  event builder, it can be seen that each N sources contains N queues, one per destination, containing the fragments of those events that have been assigned to that destination. Each destination contains N receive buffers, one receive buffer per source. Each destination receives its event fragments over N logical connections between its N receive buffers and their corresponding queue in each of the N sources. Thus, a total of  $N^2$  logical connections are required by the event builder, and at each source and destination module N different connections have to share a single interface and link to the network.

Each queue in the source can be considered as an independent "user" that transports data to another user (a destination receiver buffer) via a logical connection over a shared medium (the link) and switch. Three different transport modes can be applied to the links, namely synchronous Time Division Multiplexing (TDM), asynchronous TDM and dedicated point-to-point connections (i.e. no TDM). When synchronous or asynchronous TDM is used, the corresponding transport modes are known as Synchronous Transport Mode (STM) and Asynchronous Transport Mode

Figure 2.8: Logical model of an event builder

(ATM) <sup>2</sup> respectively. In the STM the data are transported on the link inside a fixed length *frame* which repeats indefinitely. The frame is divided into equal length time slots and each logical connection is allocated a fixed time slot in which it can transport data. Such technology was developed for telephony applications, where a constant bit-rate service is suitable to transport voice samples between subscribers at a fixed rate.

In the ATM the data are segmented into *packets*, which may be fixed or variable length, and the source sends packets over the link whenever it has data to transmit and can accesses the link. The identity of the logical connection to which the packet belongs has to be carried with it

<sup>&</sup>lt;sup>2</sup>The use of ATM to describe a generic transport mode should not be confused with the specific implementation of this transport mode in a standard technology, which is also called ATM, using fixed-length 53-Byte cells.

in the packet header, either in the form of an explicit *virtual connection* identifier (VCI) or as a pair of source and destination addresses. The ATM is well suited to handling variable bit-rate services for applications where the required bandwidth fluctuates in time.

Dedicated point-to-point connections are used in applications where concurrent transport data between multiple different "users" is not required and the source and destination can sustain data IO at the full bandwidth of the link.

Whichever of the three transport modes is used the physical bandwidth of the shared-medium limits the maximum throughput and number of "users". Multiple shared-media segments or links can be interconnected by a switch to allow communication between larger number of users. To each of the three transport modes described above there corresponds a specific class of switching technology: respectively *Circuit Switching*, *Packet Switching* and *Connection Switching*. These classes of switching technologies have quite different characteristic and application areas. Table 2.1 summarise the transport modes and classes of switching.

| Transport Mode     | Switching Class      | Characteristic                      |  |

|--------------------|----------------------|-------------------------------------|--|

| STM                | Circuit Switching    | "Telephone" switching technology    |  |

| (Synchronous TDM)  |                      | Constant bit-rate services          |  |

|                    |                      | Equal bandwidth per circuit         |  |

|                    |                      | Concurrently active circuits        |  |

| ATM                | Packet switching     | Data and multi-media switching      |  |

| (Asynchronous TDM) |                      | Burst traffic                       |  |

|                    |                      | Bandwidth allocated per connections |  |

|                    |                      | Concurrently active connections     |  |

| Dedicated links    | Connection Switching | Switching streams point-to-point    |  |

|                    |                      | Connection set up overheads         |  |

|                    |                      | Efficient for long block transfer   |  |

|                    |                      | Sequentially active connections     |  |

Table 2.1: Detector partitioning

#### 2.2.1 Circuit-switched Event Builders

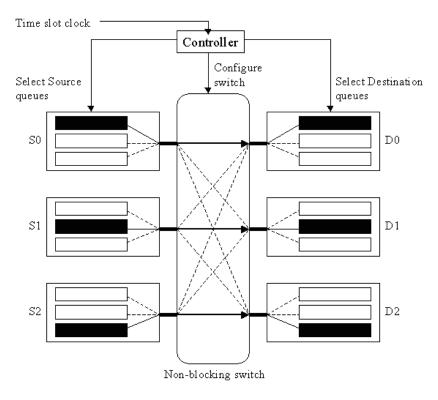

The first proposed parallel event builders were based on the same principles as circuit switching. Figure 2.9 shows how a global synchronous

control scheme is used to define time slots, in each of which circuits are set up between a different queue in each source and its corresponding receive buffer in a destination.

Figure 2.9: A circuit switched "barrel shifter" event builder

At each time slot the global controller enables the appropriate queues and receive buffers and configures the switch to route the event fragment data between them. The controller enables N circuits per slot, each one necessarily serving a different destination because only a one circuit can occupy a given slot on an output link. After N successive slots (equivalent to a frame length) all circuits will have been activated. If the slot length is chosen to be much more than the average event fragment transmission time, the scheme affectively supports the concurrent operation of  $N^2$  circuits, each offering 1/N of the link bandwidth. This scheme is often

called "barrel shifter".

If the slot length is chosen to be greater than the transmit time of the largest possible event fragment, N complete events are built every N slots. However, the typical large dispersion in the length of event fragments means that aggregate bandwidth utilisation is low because the building of a new event cannot be started until the destination has completely received all the fragments. This inefficient use of available bandwidth can be eliminated by allowing all source queues to start sending their fragment belonging to the next event in the queue before the destination has completely received all the fragments of the current event. In this case, aggregate bandwidth efficiency is optimal, but each destination has to support the building of several events simultaneously.

A necessary condition for the circuit switched barrel shifter is that circuits can always be established through the switch without blocking each other. This can be guaranteed by using a non-blocking cross-bar switch. Unfortunately, large cross-bars of the dimensions needed for LHC event builders do not exist. However, there exist certain multi-stage network topologies that, although they are not non-blocking for all possible connection patterns, do not block under particular sequences of permutations of circuits that are sufficient to perform event building [27].

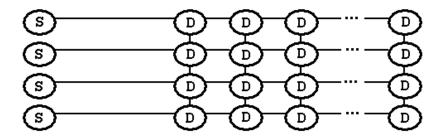

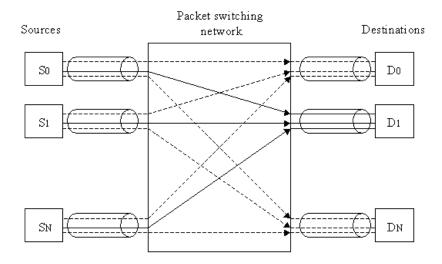

#### 2.2.2 Packet-switched Event Builders

Packet switching is more suitable for LAN traffic or multimedia applications, where the average used bandwidth of user-to-user communications may vary widely depending on the application (for example, communication versus video communication) and, for a given communication, may also fluctuate rapidly in time (for example compressed video).

The packets are routed through the multi-stage network using a label or address in the packet header. Packet switching networks use a distributed routing control paradigm in which, at each stage, look up tables map packet header information into an output port number to which the packet must be forwarded. Once these network tables have been initialised with the information that maps routing label values or addresses into the desired destination port, we have effectively set up a *virtual con-*

Figure 2.10: A packet switching event builder with permanent virtual connections fully interconnecting all sources and destinations

nection (VC). The connection is virtual because it does not reserve for itself all the resources along the path between source and destination. VCs can either be established for just as long as they are necessary to send a message (switched VCs) or they can be left in place indefinitely and only used on demand (permanent VCs). When there is no traffic flowing on a VC the network resources are available for use by traffic flowing on other VCs.

In principle the number of permanent VCs that can be set up through a network is only limited by the size of the mapping tables. Therefore a N  $\times$  N event builder can be implemented with a packet switching network by opening all the  $N^2$  VCs needed between the source queues and destination receive buffers as shown in figure 2.10.

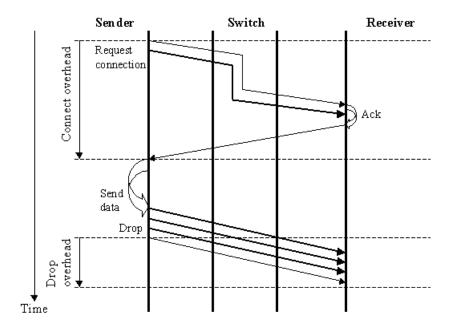

Figure 2.11 shows how, when a connection switching technology is used such as fibre channel, each source establishes a connection to the

required destination receive buffer by reserving all resources along the path. It then transmits its entire event fragment from the appropriate queue and drops the connection. The source then moves on to servicing a different queue, which requires it to disconnect from the current destination and establish a new connection to a different destination. Each request for a new connection must pass through arbitration in order to resolve contention with requests from other sources. The connection set up and drop overhead can be quite significant in some technologies.

Figure 2.11: Connect overheads in connection switching

### 2.3 Data Flow Options

As already foreseen in the previous chapter, the choice of trigger algorithms and strategies defines the data flow of the event building process.

The data flow is controlled by a protocol operating between the readout buffers (sources) and the processors (destinations).

Two different data flow control models for event building can be distinguished by whether the responsibility for initiating the transfer of event fragments is given to the sources (*push architecture*) or to the assigned destination (*pull architecture*).

In the first case the event number and the destination identifier are broadcasted to the sources, which then transmit their event fragment data to the given destination. Event builders operated in push mode are characterised by many-to-one traffic patterns and by potential contention between the many independent traffic streams. Contention occurs either for access to the output port (output blocking) or for a common internal path within the switching network. If the bandwidth of a common internal path is insufficient to handle the traffic the switch becomes congested. Output blocking and congestion have an adverse effect on the event builder's throughput and the latency of event building.

Switching technologies developed for different application domains adopt different strategies to handle contention. In the event building application the consequences of the contention handling strategy are inefficient use of the switch's bandwidth, increased event building latency, loss of data and poor scaling of performance as a function of the size of the system. Event builder performance can be optimised by using a traffic shaping technique to coordinate the traffic generated by the sources in order to minimise output blocking and internal congestion. In push mode event fragments are received at the destination out of order. Because some sources may be empty or have broken down, a mechanism is required to decide when event building is completed. An event building protocol must provide functions such as completion detection, linking fragments, etc.; this introduces software overhead.

On the other hand, an event builder operated in pull mode can use the intelligence of the destination processor to select and readout subset of the sources. The traffic patterns characterising this strategy are fewto-one, or even one-to-one, hence the negative impact of contention is much reduced compared to the push case. This approach allows early rejection of an event based on a minimum of data, and only pulls in more data for smaller number number of events that are not rejected. By applying a hierarchy of data pulls and event reject/accept decision, the overall required bandwidth of the event builder can be reduced to a minimum.

#### 2.4 Readout Protocols

Two different protocols have been studied for managing the collection of event data [24].

The first one, called the full-readout protocol, requires that data, assembled in the readout buffers, are immediately transmitted and dispatched through the readout network, such that a complete event is assembled in a destination processor. In this protocol, the buffering capacities of the destinations must be designed such that in normal operation there is always sufficient space available to receive data from readout buffers. Obviously the system must also be designed to cope with bursts of data. For this a throttle signal is sent by the readout buffers anticipating the buffer overflow, and is used to reduce the trigger rate such that the buffer occupancy can be reduced and new fragments can be accepted. The latency of the throttle signal translates into buffering requirements at the different levels of readout. The destinations collects all event fragments, and once the event is complete passes it to a processor running the high level trigger algorithms. Since all data belonging to a trigger is immediately available to the high level trigger algorithms, there is no real need in this schema to distinguish between Level-2 and Level-3. Thus the high level trigger algorithms can evolve with complete freedom.

In the second approach, called the *phased-readout protocol*, the transfer of data from the readout buffer to the high level trigger processors takes place in two or more phases <sup>3</sup>. In the first phase, the subset of the event data that is needed by Level-2 algorithm is transferred form the appropriate readout buffers to a destination processor. The data from

$<sup>^3</sup>$ More than two phases could be implemented, but this would not improve the system performance. A large number of phases would eventually result in a "data on demand" scheme

the remaining readout buffers must be buffered for the duration of Level-2 latency. The Level-2 decision must be transferred to all the readout buffers. On reception of a Level-2 "NO" decision the data are discarded, otherwise, on reception of a Level-2 "YES" decision the data must be sent to the processor that ran the Level-2 algorithm to execute further filtering algorithms (Level-3) on the complete event. As in the case of the full-readout protocol, the readout buffers will push the data to the destination processors in each phase, so again a throttle mechanism is required to prevent buffer overflows. The reduction factor of the bandwidth required of the readout network depends on the rejection power of the Level-2 algorithm and the fraction of the complete event needed to execute the algorithm. Moreover the phased readout protocol requires a new functional element called event manager. Its function is to collect the Level-2 decisions and distribute the to the appropriate readout buffers. Nevertheless the presence of an event manager would permit the dynamic load balancing across the processors of the high level triggers.

The full-readout protocol requires a larger scale readout network, but the complexity of the source modules is less than in the phased-readout case. From the point of view of simplicity of the protocols, and the flexibility it allows for the high level trigger algorithms, the full-readout protocol is preferable.

#### 2.5 Problem of Effective Throughput

Data transfer rates for networks are measured in terms of throughput, which represents the amount of data transferred from one place to another or processed in a specific amount of time. Each typology of network has its specific, well-known throughput, which is defined by the standard or the network vendor and coincides with the full use of the network bandwidth. Unfortunately this "official" maximum throughput is never reached in real life and we usually speak of effective throughput, which is the effective use of network bandwidth.

The problem of limited throughput is an important and complex question, in which a lot of factors play different roles. First of all, the most

important point to be considered is the fact that there are two big distinct factors which determine the performance of a switching network and they are the performance of point to point links and the performance of the switching network. They are quite different problems that involve further considerations and so we are going to discuss them separately in the remainder of this section.

#### 2.5.1 Effective Throughput of Point to Point Links

In the case of point to point links, our attention is concentrated only on the network access point (not really on the pure network) and throughput here is limited by several kind of overheads, which can be be grouped in two main sets:

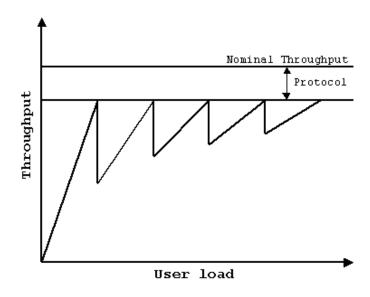

- Technology overheads (figure 2.12):

Delays, bottlenecks in network adapter...

Contention for bus control or connection setup;

Control data (headers, frame control);

"Packetisation" (partial use of fixed length packets);

Flow control...

- Software overheads (figure 2.13):

Operating system (interrupts, context switching...);

Use of additional communication protocol (like TCP/IP);

User application...

Effective throughput results from the combination of both classes of overheads.

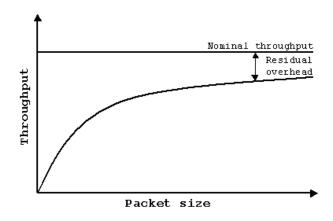

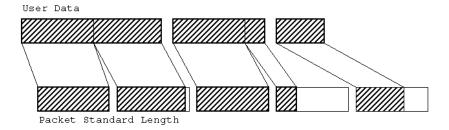

Some of these factors are unavoidable but some others can be reduced. An inevitable overhead, for example, is what we call the "packetisation" problem. This fact refers to the partial use of fixed length packets. If the network protocol requires a standard length for user data, like Ethernet, for instance, it can happen that not all packets sent through the network will be completely filled with useful data. In fact if user data size does not fit with the standard data length or its multiple, this packet field will be padded, when necessary, with useless data, with a consequent waste

Figure 2.12: Technology overheads

Figure 2.13: Software overheads

of bandwidth (figure 2.14). Of course, a variable and boundless data size would be better from the throughput point of view, but network protocols usually need a standard length and there is no possibility to avoid standard requirements.

Figure 2.14: Example of "packetisation" overheads

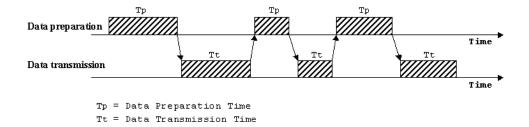

On the other hand, in order to improve the performance of point to point links, some overheads could be spared. A big improvement, for example, could be the pipe-line of data submission and data preparation. To reduce (or eliminate) the dead-time between the transmission of two packets, data that have to be sent can be prepared in the right network protocol format while ready data are transmitted. So, instead of having the bad situation described in figure 2.15 where data preparation and submission are not pipe-lined, the solution depicted in figure 2.16 could be implemented, resulting in no loss of time.

In this way the effective throughput can be improved by a reasonable factor, as figure 2.17 shows.

#### 2.5.2 Effective throughput of Network

In the case of switching networks, throughput is limited by several factors, like:

• Technology

Figure 2.15: Bad solution between data submission and data preparation

Figure 2.16: Pipeline of data submission and data preparation

Figure 2.17: Different throughput between pipe-lined and no pipe-line data submission and data preparation

- Switch architecture

- Type of traffic: random versus coherent...

The network *congestion* problem and the different techniques to avoid it play the main role in this performance study. Congestion happens when two or more data transfers compete for the same network source and there is no any mechanism to resolve this contention. In this case the throughput can be degraded and, in the worst case, data can be lost.

Two classes of technologies have been applied to prevent or to avoid congestion, namely *flow control* and *traffic shaping*. In the flow control technique, the network provides the mechanism to avoid congestion. The source sends data packets to the various destinations as soon as they are submitted and performs the operations required by the data flow mechanism. This can be:

• Back pressure, implemented on networks with internal buffering (that can store and forward);

- Collision detection, used on shared media (Ethernet);

- Connection based transfer, which consists of initiating a protocol to open an exclusive connection between source and destination, before sending any data.

Traffic shaping techniques, on the other hand, aim at subjecting the data transfer to a global traffic control thus minimising contention and congestion. There are two strategies:

- Barrel shifter, where at any one moment all sources are connected to destinations in a non blocking fashion and can send data using the full bandwidth. At regulars intervals the connections are changed (so after a full cycle (T) all sources have been connected to all destinations during a period of time T/N, being N the number of destinations);

- Rate division and randomisation, where the sources emit data in the form of small packets successively to all destinations, at an average rate per connection equal to the nominal rate divided by the number of sources.

It should be noted that all these protocols, which prevent congestion, imply lower bandwidth utilisation. Traffic shaping seems to preferable because it allows to reach high loads, whereas flow control can have several limitations depending on the network topology and on the type of traffic. At the same time, it should also be noted that, even though techniques to avoid congestion are implemented, there can be data losses. In this case a retransmission of same data is required and this implies again a throughput decrease, possibly even worse than without congestion prevention.

## Chapter 3

## Technology

A difficult issue in a physics experiment environment of the size of LHCb (and the other LHC experiments), is the choice of the appropriate technology for the event building readout network. The range of possibilities nowadays is very large, because networking industries have put big efforts in developing and improving different kinds of technologies and solutions, especially during the last ten years. An important decision is the selection between an industry standard network technology or a dedicated network system. This choice can be quite different for several reasons: each single system in fact has its own advantages and disadvantages. In the next section we will try to explain and summarise them, highlighting the different aspects. Further in the chapter, we will shortly illustrate the three technology competitors for being the final LHCb readout network technology and we will introduce the choice of this work: the Ethernet technology.

# 3.1 Industry Standards versus Dedicated Systems

The first and biggest problem for starting the building of a readout network is the decision whether to apply an industry standard network or a dedicated one. The two solutions show a lot of differences, which make

the choice difficult.

An industry standard system has its greatest advantage in the fact that it is well known and certificated, and so it can usually ensure inter-operability between different components, wide support from networking industries and scalability for future system expansions. Of course it has also a lot of boundaries due to the standard definition and it cannot be changed to meet specific requirements and needs of a particular system, like, for example, the unusual data acquisition architecture of a physics experiment.

On the other hand, a dedicated system can be modified to fit in a proper way the characteristics of a specific architecture but, of course, it does not offer any guarantee about future reliability. This kind of system in fact is strictly bound to its single vendor and thus it cannot be considered completely reliable in a long time scale. If, for some reason, its vendor crashes, all its supports will suddenly disappear.

Event building requirements can be defined quite specific and restrict and so, at a first quick view, a dedicated system, more adaptable than a standard one, could be considered the right solution. Unfortunately, it has to be taken into account that experiment lifetime is long (10–15 years) and it is necessary to guarantee adequate performance, availability and interoperability of components over a long time period. The evolution and upgrade path of the system has also to be taken into account. All these considerations make the industry standard choice more probable.

Regarding the LHCb event building switching technologies, three different solutions have been considered and investigated until today. Two of them are standards, and they are *ATM* and *Ethernet*, whereas the third one, *Myrinet*, is a dedicated system.

The remainder of the section summaries the main characteristics of these technologies and gives some suggestions for the final choice.

#### 3.1.1 ATM