## **TECHNICAL USER'S MANUAL FOR:**

# **smartModule**

# SM586PC

Nordstrasse 11/F CH- 4542 Luterbach

Tel.: ++41 (0)32 681 58 00

Fax: ++41 (0)32 681 58 01

Email: support@digitallogic.com

http://www.digitallogic.com

#### COPYRIGHT © 1999-2001 BY DIGITAL-LOGIC AG

No part of this document may be reproduced, transmitted, transcribed, stored in a retrieval system, in any form or by any means, electronic, mechanical, optical, manual, or otherwise, without the prior written permission of DIGITAL-LOGIC AG.

The software described herein, together with this document, are furnished under a license agreement and may be used or copied only in accordance with the terms of that agreement.

#### ATTENTION:

All information in this manual and the product are subject to change without prior notice.

#### **REVISION HISTORY:**

| ProdSerialnumber: |     | Product | BIOS    | Doc.    | Date/Vis:   | Modification:                |

|-------------------|-----|---------|---------|---------|-------------|------------------------------|

| From:             | To: | Version | Version | Version |             | Remarks, News, Attention:    |

|                   |     |         |         | V0.9    | 01.2001 KUF | Initial Version              |

|                   |     | V1.3    |         | V1.0    | 10.2001 KUF | Revised Version, Preliminary |

|                   |     |         |         |         |             |                              |

## **PRODUCT REGISTRATION:**

Please register your product under:

http://www.digitallogic.com -> SUPPORT -> Product Registration

After registration, you will receive driver & software updates, errata information, customer information and news from DIGITAL-LOGIC AG products automatically.

## **Table of Contents**

| 1 | Р   | REFACE                                 | .5 |

|---|-----|----------------------------------------|----|

|   | 1.1 | How to use this manual                 | 5  |

|   | 1.2 | Trademarks                             | 5  |

|   | 1.3 | Disclaimer                             | 5  |

|   | 1.4 | Who should use this product            | 5  |

|   | 1.5 | Recycling Information                  | 5  |

|   | 1.6 | SMART Support Request Form (SMART-SRF) | 6  |

|   | 1.7 | smart DesignIn Center (smart – DIC)    | 7  |

|   |     |                                        |    |

|   | 1.8<br>1.9       | Limited Warranty8 Sample Design Schematics8                              |          |

|---|------------------|--------------------------------------------------------------------------|----------|

| 2 | 2.1              | 9 VERVIEW9                                                               |          |

|   | 2.2              | Unique Features9                                                         |          |

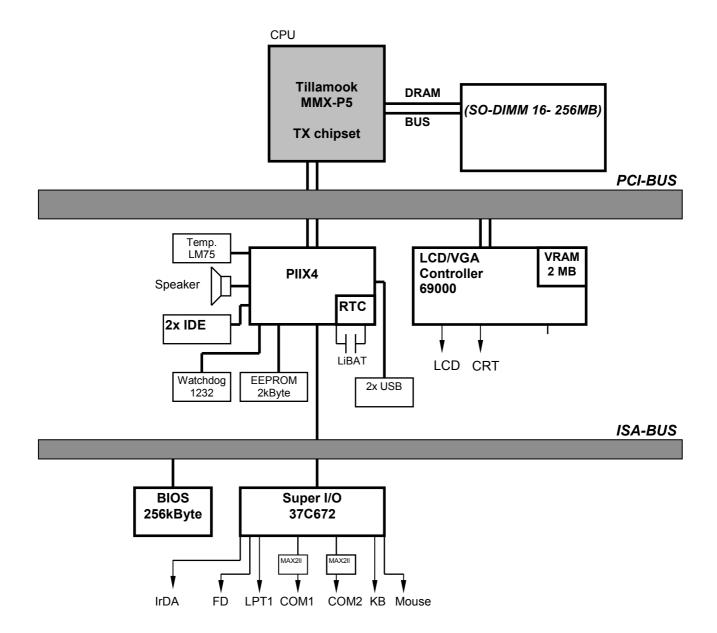

|   | 2.3              | SM586PC block diagram10                                                  |          |

|   | 2.4              | Specifications11                                                         |          |

|   | 2.5              | Ordering Codes                                                           |          |

|   | 2.6              | BIOS History                                                             |          |

|   | 2.7              | This product is "YEAR 2000 CAPABLE"                                      |          |

|   | 2.8<br>2.9       | Related Application Notes14 The smart480 bus , the future upgrade path15 |          |

|   |                  | The smartModule586PC thermoanalysis16                                    |          |

| 3 |                  | C FUNCTIONAL DESCRIPTION17                                               |          |

|   | 3.1              | Interrupt Controllers                                                    |          |

|   | 3.2              | Timers and Counters18                                                    |          |

|   |                  | .2.1                                                                     | 18       |

|   |                  | .2.2                                                                     | 19       |

|   |                  | .2.3                                                                     | 19       |

|   |                  | 3.1 ROM-BIOS                                                             | 20       |

|   |                  | 3.2EEPROM Memory for Setup                                               | 20       |

|   |                  | .3.3BIOS CMOS Setup                                                      | 21       |

|   |                  | .3.4                                                                     | 21       |

|   |                  | CMOS RAM Map22                                                           |          |

|   | 3.<br><b>3.5</b> | 4.1                                                                      | 28       |

|   | 3.6              | Download the VGA-BIOS and the CORE-BIOS                                  |          |

|   |                  | .6.1VGA BIOS Download Function                                           | 31       |

|   | 3.7              | Memory                                                                   |          |

|   |                  | .7.1System Memory Map                                                    | 32       |

|   |                  | .7.2                                                                     | 33       |

|   | 3.8              | BIOS Data Area Definitions                                               |          |

|   |                  | 9.1 VGA / LCD Controller 69000                                           | 55       |

|   |                  | 9.2VGA / LCD BIOS for 69000                                              | 55       |

|   | 3.               | 9.3                                                                      | 56       |

|   |                  | 9.4VĠA/LCD BIOS Support                                                  | 57       |

|   |                  | 9.5 Memory 69000 CRT/TFT Panels                                          | 58<br>59 |

|   | ა.<br>ვ          | .9.6                                                                     | 60       |

|   | 3.10             | The Special Function Interface (SFI)                                     | 00       |

|   | 3.               | .10.1 INT 15h SFR Functions61                                            |          |

|   |                  | Remote function (PHOENIX)67                                              |          |

|   |                  | WatchDOG Control67                                                       |          |

| 4 |                  | ESCRIPTION OF THE JUMPERS                                                |          |

|   | 4.1              | ····,····                                                                |          |

| 5 |                  | ED CRITERIONS:70                                                         |          |

|   | 5.1              |                                                                          |          |

| 6 |                  | PESIGNIN WITH THE SMARTMODULE71                                          |          |

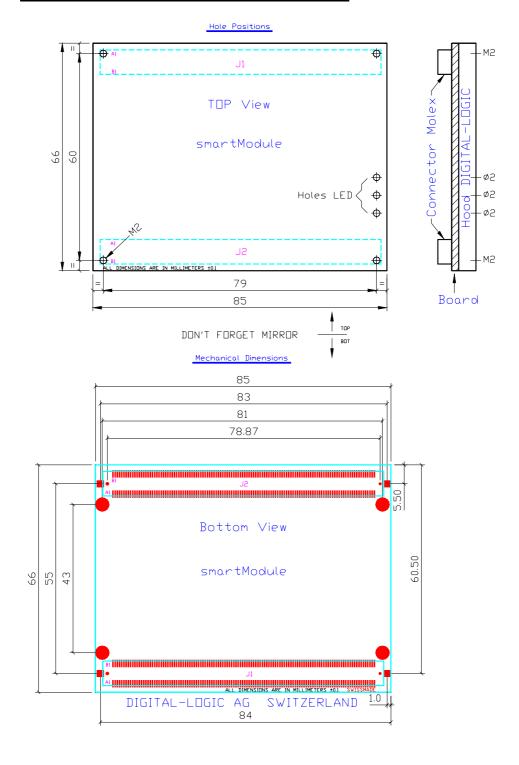

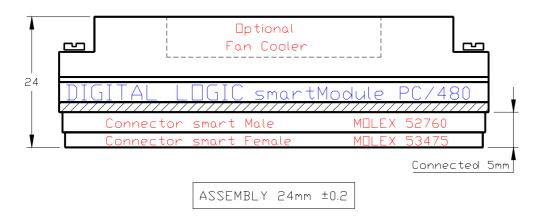

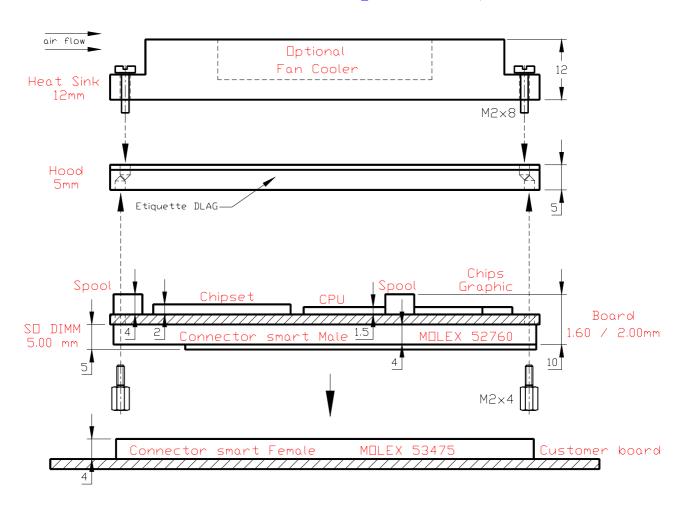

|   | <b>6.1</b>       | Mechanical Dimensions SM586PC                                            | 72       |

|   |                  | CB to SM586PC height                                                     | 12       |

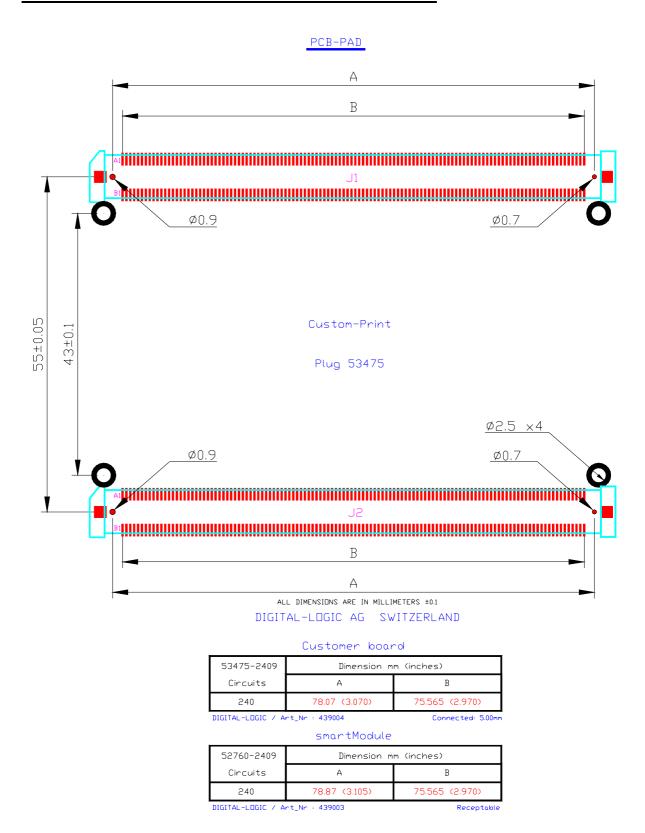

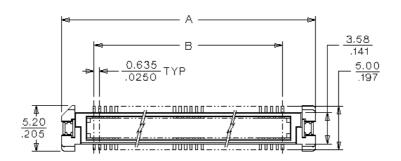

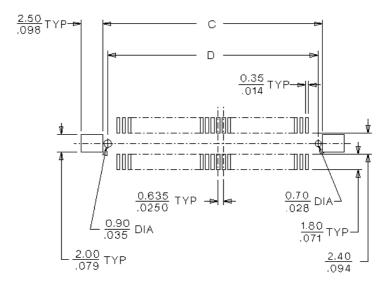

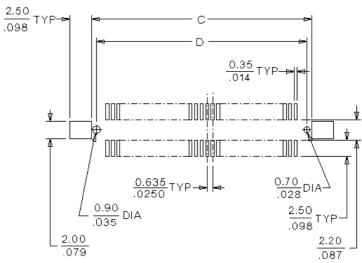

|   | 6.               | .1.3Mechanical Dimensions of the PCB, plug                               | 74       |

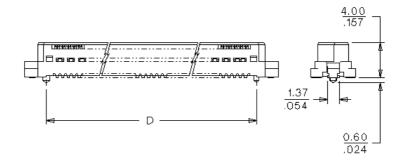

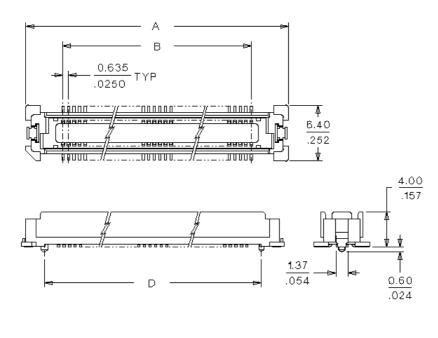

|   | 6.               | .1.4Mechanical Dimensions of the SM586PC, receptacle                     | 75       |

|   |                  | The generic smart480 bus76                                               |          |

|   |                  | 2.1 (sinceVers. 2.1) LCD Interface Signaldefinition 82                   | 76       |

|   | ช.ฮ              | LCD INTERIACE SIGNATURE INTERIOR 82                                      |          |

| 6  | CRT Monitor Signaldefinition83                       |          |

|----|------------------------------------------------------|----------|

| 6  | Connector Specifications                             |          |

| 6  | Thermal Specifications84                             |          |

| 7  | DESIGNIN BLOCK SCHEMATICS85                          |          |

| 7  | INTEL 430TX86                                        |          |

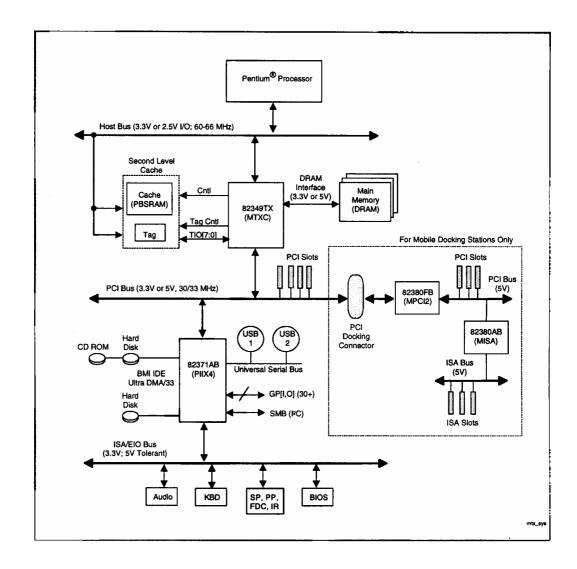

|    | .1.1Architecture overview                            | 80       |

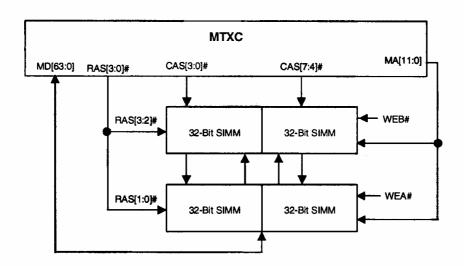

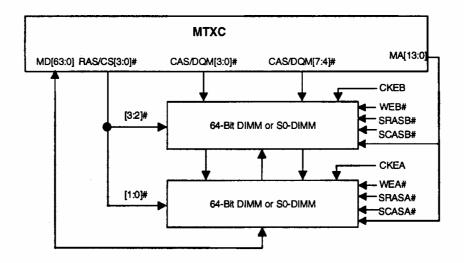

|    | .1.2DRAM Interface                                   | 80       |

|    | .1.3Second Level Cache                               | 80       |

|    | .1.4PCI Interface                                    | 86       |

|    | .1.5                                                 | 8        |

|    | .1.6Power Management Features                        | 8        |

|    | .1.7                                                 | 88       |

| _  | .1.8                                                 | 88       |

| 7  | PCI-Bus                                              | 0,       |

|    | .2.1                                                 | 89       |

|    | .2.2                                                 | 89<br>90 |

| 7  | .2.3PCI Signal Descripitons PIIX4 and Sideband-Bus92 | 90       |

| ′  | .3.1Sideband Signal Resistor Value                   | 92       |

|    | .3.2Sideband Signal Nesistor Value                   | 9;       |

| 7  | Powermanagement94                                    | ٥.       |

| •  | .4.1Power Management Signals Resistor Values         | 94       |

|    | .4.2                                                 | 9        |

| 7  | Clocks96                                             |          |

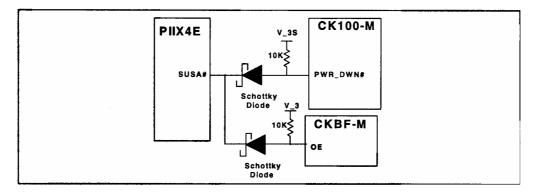

|    | .5.1                                                 | 90       |

|    | .5.2                                                 | 90       |

| 7  | ITP / JTAG Signals97                                 |          |

| 7  | Clock and Test Signals98                             |          |

| 7  | PCI Bus Signals98                                    |          |

| 7  | ISA/EIO Signals100                                   |          |

|    | Power Management Signals101                          |          |

|    | USB Interface                                        |          |

|    | IDE Interface                                        |          |

| 1  | BIOS to Flash Memory Interface                       |          |

|    | .13.1 Suspend/Resume and Power Plane Control         |          |

|    | .13.2 Power On Suspend (POS) System Model            |          |

|    | .13.4 Mechinical Off (MOff)                          |          |

|    | .13.5 System Resume                                  |          |

|    | .13.6 System Suspend and Resume Control Signaling    |          |

| 7  | PCI Devices and Definitions                          |          |

| 8  | PHOENIX – BIOS111                                    |          |

|    |                                                      |          |

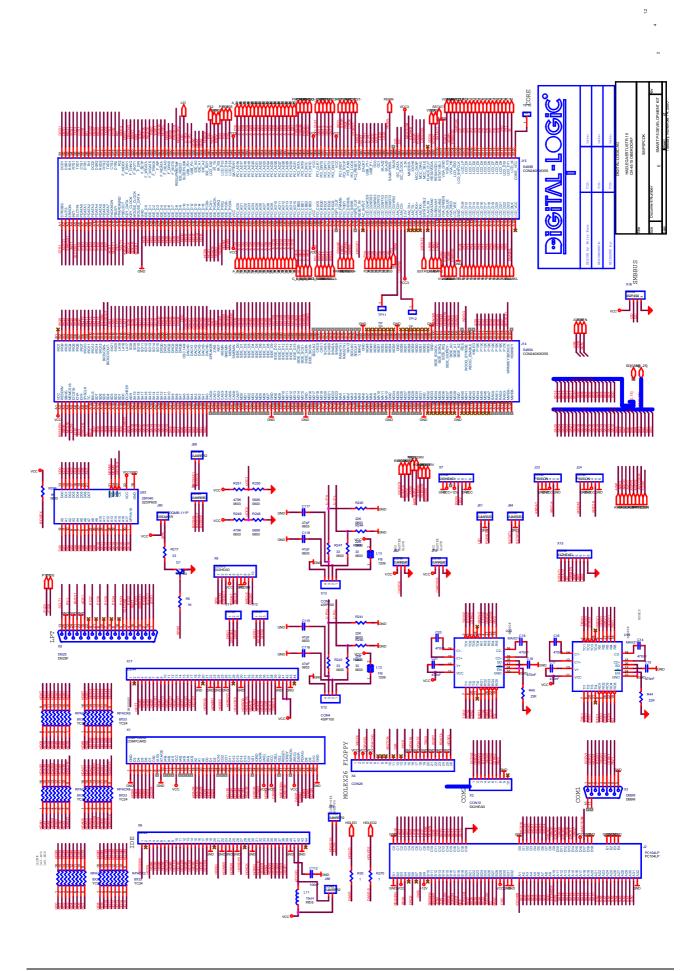

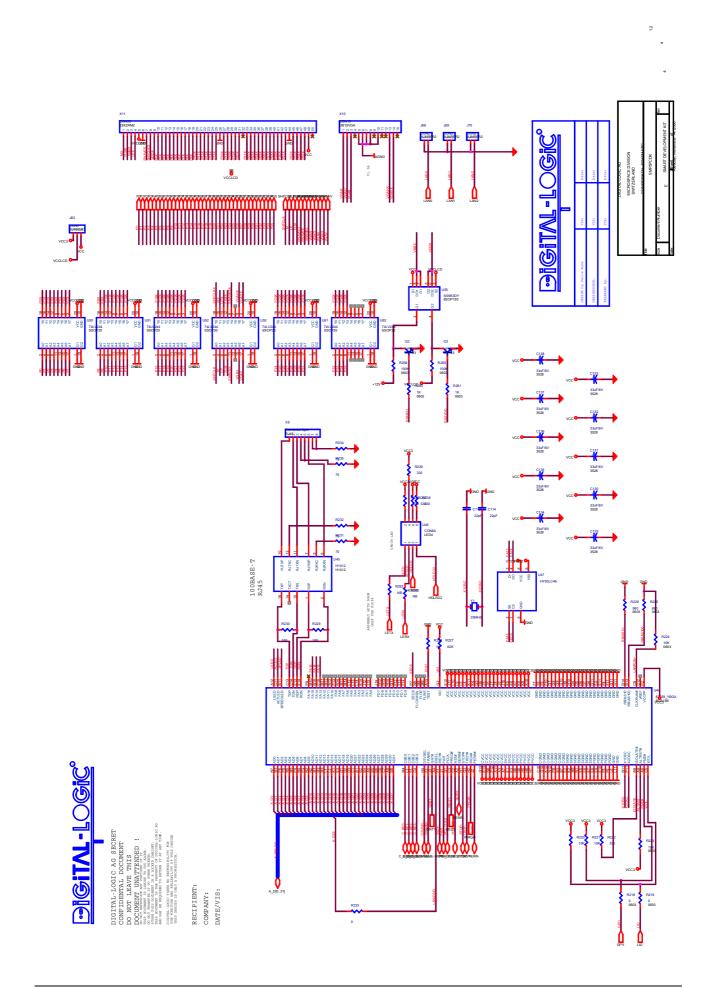

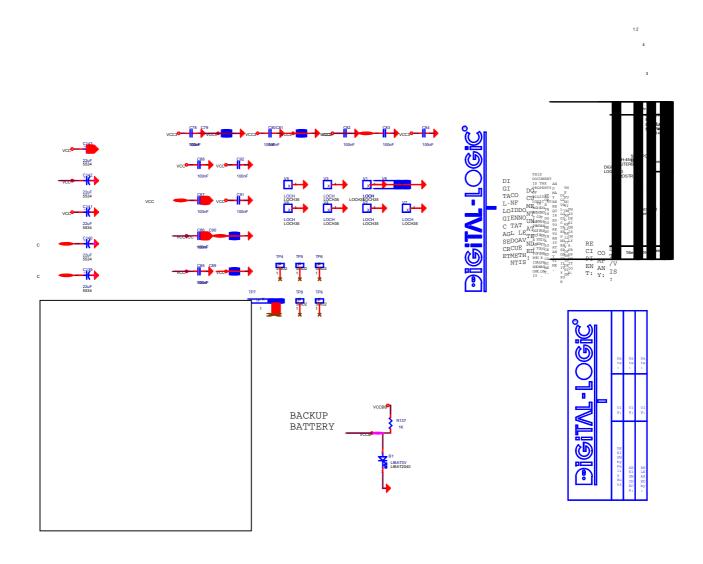

| 9  | SAMPLES SCHEMATICS SM586PC- DK112                    |          |

| 10 | NDEX116                                              |          |

## 1 Preface

This manual is for integrators and programmers of systems based on the smartModule-586PC system on chip family. It contains information on hardware requirements, interconnections, and details of how to program the system. The specifications given in this manual were correct at the time of printing; advances mean that some may have changed in the meantime.

## 1.1 How to use this manual

This manual is written for the original equipment manufacturer (OEM) who plans to build computer systems based on the system on chip units. It provides instructions for designing, installing and configuring the unit, and describes the system and setup requirements.

#### 1.2 <u>Trademarks</u>

Chips & Technologies SuperState R

MICROSPACE, MicroModule DOS Vx.y, Windows DIGITAL-LOGIC AG

Microsoft Inc.

PC-AT, PC-XT IBM

NetWare Novell Corporation Ethernet Xerox Corporation

DR-DOS, PALMDOS Digital Research Inc. / Novell Inc.

ROM-DOS Datalight Inc.

#### 1.3 Disclaimer

DIGITAL-LOGIC AG makes no representations or warranties with respect to the contents of this manual and specifically disclaims any implied warranty of merchantability or fitness for any particular purpose. DIGITAL-LOGIC AG shall under no circumstances be liable for incidental or consequential damages or related expenses resulting from the use of this product, even if it has been notified of the possibility of such damage. DIGITAL-LOGIC AG reserves the right to revise this publication from time to time without obligation to notify any person of such revisions

## 1.4 Who should use this product

- Electronic engineers with know-how in PC-technology.

- Without electronic know-how we expect you to have questions. This manual assumes, that you have a

general knowledge of PC-electronics.

- Because of the complexity and the variability of PC-technology, we can't give any warranty that the product will work in any particular situation or combination.

- Pay attention to the electrostatic discharges. Use a CMOS protected workplace.

- Power supply OFF when you are working on the board or connecting any cables or devices.

# This is a high technology product. You need know-how in electronics and PC-technology to install the system!

## 1.5 <u>Recycling Information</u>

**Hardware:**

- **Print**: epoxy with glass fiber

wires are of tin-plated copper

- Components: ceramics and alloys of gold, silver

check your local electronic recycling

## 1.6 <u>SMART Support Request Form (SMART-SRF)</u>

1. Send this SRF with your problem description to:

DIGITAL-LOGIC AG

smartModule DesignIn Center

Nordstr. 11/F

CH-4542 Luterbach (SWITZERLAND)

Fax: ++41 32 681 58 01

E-Mail: support@digitallogic.com

Internet www.digitallogic.com

Support request form (fill in and send via fax to DIGITAL-LOGIC AG support center):

| SRF No:             | S118               | Date:              |   |

|---------------------|--------------------|--------------------|---|

|                     |                    | Customer company:  |   |

| Customer Name:      |                    |                    |   |

| Customer Tel.No.:   |                    | Customer E-Mail:   |   |

| Customers           |                    | Customers Country: |   |

| Address:            |                    |                    |   |

| SMART type:         | SM586PC            | processing date:   |   |

| Request type:       | Support Report:    | Operating System:  |   |

|                     | DesignIn Aid:      | OS Version:        | V |

|                     | BIOS Adaption:     | BIOS Version:      | V |

|                     | Manual Correction: |                    |   |

|                     | others:            |                    |   |

|                     |                    |                    |   |

| Problem description | n:                 |                    |   |

| Problem description:                                                             |

|----------------------------------------------------------------------------------|

|                                                                                  |

|                                                                                  |

|                                                                                  |

|                                                                                  |

|                                                                                  |

|                                                                                  |

|                                                                                  |

| Solution / Answer (will be filled in by DIGITAL-LOGIC AG SMART DesignIn center): |

|                                                                                  |

|                                                                                  |

|                                                                                  |

|                                                                                  |

| Support date: |     |    | Support statistics:                       |              |

|---------------|-----|----|-------------------------------------------|--------------|

| Support sign: |     |    | Comment:                                  |              |

| Support cost: | yes | no | Offered costs for serving design support: | CHF/USD/DEM: |

| DesignIn No.: |     |    | Effective time / costs:                   |              |

## 1.7 <u>smart DesignIn Center (smart – DIC)</u>

DIGITAL-LOGIC AG offers a DesignIn support from a specialized engineering group in the SMART DesignIn Center (SMART – DIC). To initialize a DesignIn Support, please fill in the SMART-SRF form. The DesignIn Support can be offered in each phase of a DesignIn procedure. Only the ordered support value will be charged. The charge fees are as follow:

| Design Phase No. |    | Support type                                | Fee      | Charged   |

|------------------|----|---------------------------------------------|----------|-----------|

|                  |    |                                             |          |           |

| Evaluation       | 01 | Consultation                                | CHF 200  | per hour  |

|                  | 02 | Training                                    | CHF 200  | per hour  |

|                  | 03 | Design of the customers specification       | CHF 150  | per hour  |

|                  |    |                                             |          |           |

| Schematics       | 10 | Consultation                                | CHF 200  | per hour  |

|                  | 11 | Design of the schematics                    | CHF 150  | per hour  |

|                  | 12 | Review / Inspection of customers schematics | CHF 300  | per sheet |

|                  | 13 | Development of circuits / schematics        | CHF 200  | per hour  |

|                  |    |                                             |          |           |

| Layout           | 20 | Consultation                                | CHF 200  | per hour  |

|                  | 21 | Design of the layout                        | CHF 150  | per hour  |

|                  | 22 | Review / Inspection of customers layout     | CHF 300  | per sheet |

|                  | 23 | Development of circuits / layout            | CHF 200  | per hour  |

| BIOS             | 30 | Consultation                                | CHF 200  | per hour  |

| 5.00             | 31 | Modification / Test of the BIOS sourcecode  | CHF 1500 | per day   |

|                  | 32 | Review / Inspection of customers software   | CHF 300  | per hour  |

|                  | 33 | Development of software                     | CHF 200  | per hour  |

|                  |    |                                             |          |           |

| Prototype        | 40 | Consultation                                | CHF 200  | per hour  |

|                  | 41 | Test of customers system                    | CHF 1200 | per day   |

|                  | 42 | Review / Inspection of customers system     | CHF 300  | per hour  |

|                  | 43 | Development of test entvironment            | CHF 200  | per hour  |

All costs are payable in advance.

## 1.8 <u>Limited Warranty</u>

DIGITAL-LOGIC AG warrants the hardware and software products it manufactures and produces to be free from defects in materials and workmanship for one year following the date of shipment from DIGITAL-LOGIC AG, Switzerland. This warranty is limited to the original purchaser of product and is not transferable.

During the one year warranty period, DIGITAL-LOGIC AG will repair or replace, at its discretion, any defective product or part at no additional charge, provided that the product is returned, shipping prepaid, to DIGITAL-LOGIC AG. All replaced parts and products become property of DIGITAL-LOGIC AG.

#### Before returning any product for repair, customers are required to contact the company.

This limited warranty does not extend to any product which has been damaged as a result of accident, misuse, abuse (such as use of incorrect input voltages, wrong cabling, wrong polarity, improper or insufficient ventilation, failure to follow the operating instructions that are provided by DIGITAL-LOGIC AG or other contingencies beyond the control of DIGITAL-LOGIC AG), wrong connection, wrong information or as a result of service or modification by anyone other than DIGITAL-LOGIC AG. Neither, if the user has not enough knowledge of these technologies or has not consulted the product manual or the technical support of DIGITAL-LOGIC AG and therefore the product has been damaged.

Except, as expressly set forth above, no other warranties are expressed or implied, including, but not limited to, any implied warranty of merchantability and fitness for a particular purpose, and DIGITAL-LOGIC AG expressly disclaims all warranties not stated herein. Under no circumstances will DIGITAL-LOGIC AG be liable to the purchaser or any user for any damage, including any incidental or consequential damage, expenses, lost profits, lost savings, or other damages arising out of the use or inability to use the product.

## 1.9 <u>Sample Design Schematics</u>

DIGITAL-LOGIC AG offers all schematics as a design guide only. DIGITAL-LOGIC AG assumes no responsibility for final system design. It is also assumed, that the designer has the reference manual of the PENTIUM chip, the programmers reference from the PENTIUM chip. DIGITAL-LOGIC AG assumes, that the designer of a smartModule-586PC design, has the knowledge of designing ISA based PC architecture.

## 2 OVERVIEW

## 2.1 <u>Features</u>

The smartModule-586PC is a miniaturized PC system on chip unit incorporating the major elements of a PC/AT compatible computer. It includes standard PC/AT compatible elements, such as:

- Powerful X86

- BIOS ROM (since V2.0 soldered)

- SODIMM socket for 16 128MB

- Timers

- DMA

- Real-time clock

- 2k EEPROM

- LPT1

- COM1, COM2

- Speaker interface

- AT-keyboard interface

- PS/2 mouse interface

- Floppydisk interface

- 2x ATA-IDE harddisk interface

- VGA/LCD video controller

- Embedded smartBUS480

- 3.3V power supply (switched mode)

## 2.2 Unique Features

- EEPROM for setup and configuration

- UL approved parts

\_

## 2.3 SM586PC block diagram

## 2.4 <u>Specifications</u>

| CPU: |

|------|

|------|

| CPU:                 | MachZF 586 133MHz       |

|----------------------|-------------------------|

| Mode:                | Real / Protected        |

| Compatibility:       | 8086 – 80386            |

| 1. Level Cache:      | 16 & 16kByte write-back |

| Word Size:           | 64 Bits                 |

| Physical Addressing: | 32 lines                |

| Virtual Addressing:  | 64 Mbytes               |

| Clock Rates:         | 133 MHz selectable      |

#### Math. Coprocessor:

Available on the CPU -

#### **Power Management:**

available Defined by the PHOENIX BIOS

#### DMA:

8237A comp. 2 channels 8 Bits

#### Interrupts:

8259 comp. 8 + 2 levels PC compatible

#### Timers:

8254 comp. 3 programmable counter/timers

#### Memory:

DRAM SODIMM 144pin holder (16 – 128Mbyte), external expandable

#### Video:

Controller: 69000 PCI-BUS

CRT: 2Mbyte

LCD: up to 1024 x 768 x 256 colors Panel: TFT 24Bit, STN, EL Plasma

#### Mass Storage:

| FD: | Floppy disk interface, for max. 2 floppy          |

|-----|---------------------------------------------------|

| HD: | 2x IDE interface, AT - Type, for max. 4 harddisks |

#### Standard AT Interfaces:

| Serial: | Device | FIFO |      | Addr. | Signals: | Remarks |

|---------|--------|------|------|-------|----------|---------|

|         | Name   |      | IRQs |       |          |         |

|         | COM1   | yes  | IRQ4 | 3F8   |          |         |

|         | COM2   | yes  | IRQ3 | 2F8   |          |         |

(Baudrates: 50 – 115 KBaud programmable)

| Parallel:       | LPT1 printer interface, Modes: SPP (output) , EPP ( bidir.) |  |  |

|-----------------|-------------------------------------------------------------|--|--|

| Keyboard:       | AT- or PS/2-keyboard                                        |  |  |

| Mouse:          | PS/2                                                        |  |  |

| Speaker:        | 0.1 W output drive                                          |  |  |

| RTC:            | Integrated into the PIIX4 with CMOS-RAM 256byte             |  |  |

| Backup current: | <5 μA at 3V                                                 |  |  |

| Battery:        | Not assembled                                               |  |  |

#### Supervisory:

Watchdog: LTC1232 with power-fail detection, strobe time max. 1 sec.

#### BUS:

| ISA:       | IEEE-996 standard bus           |  |  |

|------------|---------------------------------|--|--|

| Clock:     | 8 MHz                           |  |  |

| PC/104plus | IEEE-996 standard bus, buffered |  |  |

| Clock:     | 10 MHz defined by the PIIX4     |  |  |

| USB        | Defined by the PIIX4            |  |  |

| DRAM       | Defined by the PIIX4            |  |  |

#### Power Supply:

Working: 5 Volts  $\pm$  5%, 3.3V onboard switch mode regulator Power Rise Time: >  $100\mu s$  (0V --> 4,75V)

#### **Physical Characteristics:**

Dimensions: Length: 85 mm +/- 0.1 mm

Depth: 66 mm +/- 0.1mm

Height: 16 mm +/- 0.2mm (with 5mm bus connectors)

| Weight:        | 90 gr / 9 ounces               |

|----------------|--------------------------------|

| PCB Thickness: | 1.6 mm / 0.0625 inches nominal |

| PCB Layer:     | Multilayer                     |

#### Operating Environment:

| Relative Humidity: | 5 - 90% non condensing |                                                                                                                                     |  |

|--------------------|------------------------|-------------------------------------------------------------------------------------------------------------------------------------|--|

| Vibration:         | 5 to 2000 Hz           |                                                                                                                                     |  |

| Shock:             | 10 G                   |                                                                                                                                     |  |

| Temperature:       | Operating:             | Standard version 166MHz: -25°C to +70###C (with a 266MHz only 60°C, or 70°C if clk reduced!) Extended version: -40°C to +85°C T.B.A |  |

|                    | Storage:               | -55°C to +85 ###C                                                                                                                   |  |

| EMI / EMC (IEC1131-2 refer MIL 461/462): |                                                                                                                        |                                                                                |

|------------------------------------------|------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|

| ESD Electro Static Discharge:            | IEC 801-2, EN55101-2, VDE 0843/0847 Part 2 metallic protection needed separate Ground Layer included 15 kV single peak |                                                                                |

| REF Radiated Electromagnetic Field:      | IEC 801-3, VDE 0843 Part 3, IEC770 6.2.9. not tested                                                                   |                                                                                |

| EFT Electric Fast Transient (Burst):     | IEC 801-4, EN50082-1, VDE 0843 Part 4<br>250V - 4kV, 50 ohms, Ts=5ns<br>Grade 2: 1KV Supply, 500 I/O, 5Khz             |                                                                                |

| SIR Surge Immunity Requirements:         |                                                                                                                        | E587, VDE 0843 Part 5<br>2 kV, 6 pulse/minute<br>500 V, 2 pulse/minute<br>none |

| High-frequency radiation:                | EN55022                                                                                                                |                                                                                |

Any information is subject to change without notice.

## 2.5 <u>Ordering Codes</u>

SM586PC-133 smartModule586PC, 133MHz, 0MB

SMxxPC-DK-32 smartModulexxPC Development-Kit with 32Mbyte DRAM

## 2.6 BIOS History

| Version: | Date: | Status: | Modifications: |

|----------|-------|---------|----------------|

|          |       |         |                |

|          |       |         |                |

|          |       |         |                |

|          |       |         |                |

|          |       |         |                |

## 2.7 This product is "YEAR 2000 CAPABLE"

This DIGITAL-LOGIC product is "YEAR 2000 CAPABLE". This means, that upon installation, it accurately stores, displays, processes, provides and/or receives date data from, into, and between 1999 and 2000, and the 20. and 21. centuries, including leap year calculations, provided that all other technology used in combination with said product properly exchanges date data with it. DIGITAL-LOGIC makes no representation about individual components within the product should be used independently from the product as a whole. You should understand that DIGITAL-LOGIC's statement that an DIGITAL-LOGIC product is "YEAR 2000 CAPABLE" means only that DIGITAL-LOGIC has verified that the product as a whole meets this definition when tested as a stand-alone product in a test lab, but does not mean that DIGITAL-LOGIC has verified that the product is "YEAR 2000 CAPABLE" as used in your particular situation or configuration. DIGITAL-LOGIC makes no representation about individual components, including software, within the product should they be used independently from the product as a whole.

DIGITAL-LOGIC customers use DIGITAL-LOGIC products in countless different configurations and in conjunction with many other components any systems, and DIGITAL-LOGIC has no way to test whether all those configurations and systems will properly handle the transition to the year 2000. DIGITAL-LOGIC encourages its customers and others to test whether their own computer systems and products will properly handle the transition to the year 2000.

The only proper method of accessing the date in systems is indirectly from the Real-Time-Clock via the BIOS. The BIOS in DIGITAL-LOGIC computerboards contains a century checking and maintenance feature the checks the laest two significant digits of the year stored in the RTC during each BIOS request (INT 1A) to read the date and, if less than '80' (i.e. 1980 is the first year supported by the PC), updates the century byte to '20'. This feature enables operating systems and applications using BIOS date/time services to reliably manipulate the year as a four-digit value.

## 2.8 Related Application Notes

| # | Description |

|---|-------------|

|   |             |

|   |             |

|   |             |

|   |             |

|   |             |

|   |             |

→ Application Notes re availble at <a href="http://www.digitallogic.com">http://www.digitallogic.com</a> ->support, or on any Application CD from DIGITAL-LOGIC.

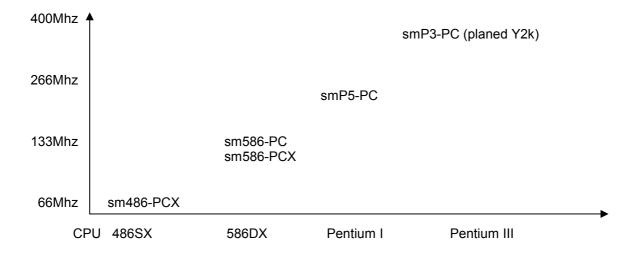

## 2.9 The smart480 bus, the future upgrade path

DIGITAL-LOGIC produces different smartmodules using the smart480 bus. Since each module has some unique features, the integrator must use this signals carefully, if he likes to upgrade lateron with another module with a higher performance.

The following performance will be available:

| CPU                 | 486SX (ELAN400) | 586DX       | Pentium I   | Pentium III |

|---------------------|-----------------|-------------|-------------|-------------|

| CPU-Clock           | 33-99Mhz        | 133Mhz      | 166-266Mhz  | 400-500Mhz  |

| Power consumption   | 3 - 4 Watts     | 3 - 5 Watts | 5 – 7 Watts | 7 – 9 Watts |

|                     |                 |             |             |             |

| Standard functions  |                 |             |             |             |

| DRAM Expansion      | 32Bit           | 32Bit       | 64Bit       | 64Bit       |

| Keyboard & Mouse    | yes             | yes         | yes         | yes         |

| COM1                | yes             | yes         | yes         | yes         |

| COM2                | yes             | yes         | yes         | yes         |

| Floppydisk          | yes             | yes         | yes         | yes         |

| LPT1                | yes             | yes         | yes         | yes         |

| Prim-IDE            | yes             | yes         | yes         | yes         |

| Sec-IDE             | no              | yes         | yes         | yes         |

| ISA-Bus             | yes             | yes         | yes         | yes         |

| CRT-VGA Signals     | yes             | yes         | yes         | yes         |

| LCD 24Bit           | yes             | yes         | yes         | yes         |

|                     |                 |             |             |             |

| Unique functions:   |                 |             |             |             |

| PCCard              | yes             | no          | no          | no          |

| LAN                 | yes             | no          | no          | no          |

| PCI-Bus             | no              | yes         | yes         | yes         |

| Keymatrix           | yes             | no          | no          | no          |

| 1/4VGA LCD          | yes             | no          | no          | no          |

| 36Bit LCD Extension | no              | yes         | yes         | yes         |

| USB Interface       | no              | no          | yes         | yes         |

| COM3                | yes             | no          | no          | no          |

| ZV-Port             | no              | no          | no          | no          |

## 2.10 The smartModule586PC thermoanalysis

DIGITAL-LOGIC provides a set of thermal images, made after 60min operating in a typical applications.

Without cooler:

## 3 PC FUNCTIONAL DESCRIPTION

## 3.1 <u>Interrupt Controllers</u>

An 8259A compatible interrupt controller, within the TX chipset, provides seven prioritized interrupt levels. Of these, several are normally associated with the board's onboard device interfaces and controllers, and several are available on the AT expansion bus.

| Interrupt: | Sources:                                   | onboard used: |

|------------|--------------------------------------------|---------------|

| IRQ0       | ROM-BIOS clock tick function, from timer 0 | yes           |

| IRQ1       | Keyboard controller output buffer full     | yes           |

| IRQ2       | Used for cascade 2. 8259                   | yes           |

| IRQ3       | COM2 serial port                           | yes           |

| IRQ4       | COM1 serial port                           | yes           |

| IRQ5       | LPT2 parallel printer (if present)         | no *          |

| IRQ6       | Floppy controller                          | yes           |

| IRQ7       | LPT1 parallel printer                      | yes           |

| IRQ8       | Battery backed clock                       | yes           |

| IRQ9       | Free for user                              | no *          |

| IRQ10      | Free for user                              | no *          |

| IRQ11      | Free for user                              | no *          |

| IRQ12      | PS/2 mouse                                 | yes           |

| IRQ13      | Math. coprocessor                          | yes           |

| IRQ14      | Harddisk IDE / SCSI yes                    |               |

| IRQ15      | Free for user no *                         |               |

<sup>- \*</sup> It may depends on the LAN configuration

## 3.2 Timers and Counters

#### 3.2.1 **Programmable Timers**

An 8253 compatible timer/counter device is also included in the board's ASIC device. This device is utilized in precisely the same manner as in a standard AT implementation. Each channel of the 8253 is driven by a 1.190 MHz clock, derived from a 14.318 MHz oscillator, which can be internally divided in order to provide a variety of frequencies.

Timer 2 can also be used as a general purpose timer if the speaker function is not required.

#### **Timer Assignment**

| Timer | Function                            |

|-------|-------------------------------------|

| 0     | ROM-BIOS clock tick (18.2 Hz)       |

| 1     | DRAM refresh request timing (15 µs) |

| 2     | Speaker tone generation time base   |

#### 3.2.2 Battery backed clock (RTC)

An AT compatible date/time clock is located within the chipset. The device also contains a CMOS static RAM, compatible with that in standard ATs. System configuration data is normally stored in the clock chip's CMOS RAM in a manner consistent with the convention used in other AT compatible computers.

Connect an external Lithium battery of 3V to the RTC pin.

The battery-backed clock can be set by using the DIGITAL-LOGIC AG SETUP at boot-time.

Addresses: 70h = Index register

71h = Data transfer register

RTC-Address MAP: 00 - 0F Real time clock

10 - 3F BIOS setup (Standard)

40 - 7F Extended BIOS

With an external Lithium 3V- battery, the board is able to work over 10 years without replacing. The chip set consumes the following currents:

Typical battery current at 25°C: <5 µA

#### 3.2.3 Watchdog

#### **3.3 BIOS**

#### **3.3.1 ROM-BIOS**

An EPROM with 8 Bit wide data access normally contains the board's AT compatible ROM-BIOS. The BIOS takes a 29C020 EPROM (or equivalent) device. The board's wait-state control logic automatically inserts four memory wait states in all CPU accesses to this (socket). The ROM-BIOS occupies the memory area from C0000H through FFFFFh; however, the board's ASIC logic reserves the entire area from C0000h through FFFFFh for onboard devices, so that this area is already usable for ROM-DOS and BIOS expansion modules.

Consult the appropriate address map for the MICROSPACE SM586PC ROM-BIOS.

#### 3.3.1.1 Standard BIOS ROM

DEVICE: 29C020 PLCC32

MAP: E0000 - FFFFFh BIOS from PHOENIX, 256kB onboard soldered

C0000 - CBFFFh VGA BIOS from Chips & Technology 32kB or 44kB

CC000 - CFFFFh reserved

#### 3.3.2 **EEPROM Memory for Setup**

The EEPROM is used for setup and configuration data, stored as an alternative to the CMOS-RTC. Optionally, the EEPROM setup driver may update the CMOS RTC, if the battery is running down and the checksum error would appear and stop the system. The capacity of the EEPROM is 2 kByte.

Organisation of the 2048Byte EEPROMs:

| Address MAP: | Function:                                                                  |

|--------------|----------------------------------------------------------------------------|

| 0000h        | CMOS-Setup valid (01=valid)                                                |

| 0001h        | Keymatrix-Setup valid (01=valid)                                           |

| 0003h        | Flag for DLAG-Message (FF=no message)                                      |

| 0010h-007Fh  | Copy of CMOS-Setup data                                                    |

| 0080h-00FFh  | reserved for AUX-CMOS-Setup                                                |

| 0100h-010Fh  | Serial-Number                                                              |

| 0110h-0113h  | Production date (year/day/month)                                           |

| 0114h-0117h  | 1. Service date (year/day/month)                                           |

| 0118h-011Bh  | 2. Service date (year/day/month)                                           |

| 011Ch-011Fh  | 3. Service date (year/day/month)                                           |

| 0120h-0122h  | Booterrors (Autoincremented if any booterror occurs)                       |

| 0123h-0125h  | Setup Entries (Autoincremented on every Setup entry)                       |

| 0126h-0128h  | Low Battery (Autoincremented everytime the battery is low, EEPROM -> CMOS) |

| 0129h-012Bh  | Startup (Autoincremented on every poweron start)                           |

| 0130h        | Number of 512k SRAM                                                        |

| 0131h        | Number of 512k Flash                                                       |

| 0132h/0133h  | BIOS Version (V1.4 => [0132h]:= 4, [0133h]:=1)                             |

| 0134h/0135h  | BOARD Version (V1.5 => [0124h]:=5, [0125h]:=1)                             |

| 0136h        | BOARD TYPE ('M'=PC/104, 'E'=Euro, 'W'=MSWS, 'S'=Slot, 'C'=Custom)          |

| 0137h        | CPU TYPE                                                                   |

|              | (01h=ELAN300/310, 02h=ELAN400, 03h=486SLC, 04h=486DX, 05h=P5).             |

| 0200h-03FFh  | Keymatrix-Setup data                                                       |

| 0200h-027Fh  | Keymatrix Table                                                            |

| 0400h-07FFh  | Free for Customer's use                                                    |

#### 3.3.3 BIOS CMOS Setup

If wrong setups are memorized in the CMOS-RAM, the default values will be loaded after resetting the RTC/CMOS-RAM with the CMOS-RESET jumper. If the battery is down, it is always possible to start the system with the default values from the BIOS.

#### **WARNING:**

On the next setup pages (switch with TAB) the values for special parameters are modifiable. Normally the parameters are set correctly by DIGITAL-LOGIC AG. Be very careful in modifying any parameter since the system could crash. Some parameters are dependent on the CPU type. The cache parameter is always available, for example. So, if you select too few wait states, the system will not start until you reset the CMOS-RAM using the RAM-Reset jumper, but the default values are reloaded. If you are not familiar with these parameters, do not change anything!

#### 3.3.4 CMOS Setup Harddisk List

Use type 48 and type 49 for user defined harddisk entries. Enter the sectors, cylinders and the number of heads. Select AUTODETECT in order to autoidentify the harddisk parameters.

## 3.4 CMOS RAM Map

Systems based on the industry-standard specification include a battery backed Real Time Clock chip. This clock contains at least 64 bytes of non-volatile RAM. The system BIOS uses this area to store information including system configuration and initialization parameters, system diagnostics, and the time and date. This information remains intact even when the system is powered down.

The BIOS supports 128 bytes of CMOS RAM. This information is accessible through I/O ports 70h and 71h. CMOS RAM can be divided into several segments:

- Locations 00h 0Fh contain real time clock (RTC) and status information

- Locations 10h 2Fh contain system configuration data

- Locations 30h 3Fh contain System BIOS-specific configuration data as well as chipset-specific information

- Locations 40h 7Fh contain chipset-specific information as well as power management configuration parameters

The following table provides a summary of how these areas may be further divided.

| Beginning | Ending | Checksum | Description                         |

|-----------|--------|----------|-------------------------------------|

| 00h       | 0Fh    | No       | RTC and Checksum                    |

| 10h       | 2Dh    | Yes      | System Configuration                |

| 2Eh       | 2Fh    | No       | Checksum Value of 10h - 2Dh         |

| 30h       | 33h    | No       | Standard CMOS                       |

| 34h       | 3Fh    | No       | Standard CMOS - SystemSoft Reserved |

| 40h       | 5Bh    | Yes      | Extended CMOS - Chipset Specific    |

| 5Ch       | 5Dh    | No       | Checksum Value of 40h - 5Bh         |

| 5Eh       | 6Eh    | No       | Extended CMOS - Chipset Specific    |

| 6Fh       | 7Dh    | Yes      | Extended CMOS - Power Management    |

| 7Eh       | 7Fh    | No       | Checksum Value of 6Fh - 7Dh         |

| Location | Description                                                                                  |  |  |

|----------|----------------------------------------------------------------------------------------------|--|--|

| 00h      | Time of day (seconds) specified in BCD                                                       |  |  |

| 01h      | Alarm (seconds) specified in BCD                                                             |  |  |

| 02h      | Time of Day (minutes) specified in BCD                                                       |  |  |

| 03h      | Alarm (minutes) specified in BCD                                                             |  |  |

| 04h      | Time of Day (hours) specified in BCD                                                         |  |  |

| 05h      | Alarm (hours) specified in BCD                                                               |  |  |

| 06h      | Day of week specified in BCD                                                                 |  |  |

| 07h      | Day of month specified in BCD                                                                |  |  |

| 08h      | Month specified in BCD                                                                       |  |  |

| 09h      | Year specified in BCD                                                                        |  |  |

| 0Ah      | Status Register A                                                                            |  |  |

|          | Bit 7 = Update in progress                                                                   |  |  |

|          | Bits 6-4 = Time based frequency divider                                                      |  |  |

|          | Bits 3-0 = Rate selection bits that define the periodic interrupt rate and output frequency. |  |  |

| 0Bh      | Status Register B                                                                            |  |  |

|          | Bit 7 = Run/Halt                                                                             |  |  |

|          | 0 Run                                                                                        |  |  |

|          | 1 Halt<br>Bit 6 = Periodic Timer                                                             |  |  |

|          | 0 Disable                                                                                    |  |  |

|          | 1 Enable                                                                                     |  |  |

|          | Bit 5 = Alarm Interrupt 0 Disable                                                            |  |  |

|          | 1 Enable                                                                                     |  |  |

|          | Bit 4 = Update Ended Interrupt                                                               |  |  |

|          | 0 Disable<br>1 Enable                                                                        |  |  |

|          | Bit 3 = Square Wave Interrupt                                                                |  |  |

|          | 0 Disable                                                                                    |  |  |

|          | 1 Enable<br>Bit 2 = Calendar Format                                                          |  |  |

|          | 0 BCD                                                                                        |  |  |

|          | 1 Binary                                                                                     |  |  |

|          | Bit 1 = Time Format<br>0 12-Hour                                                             |  |  |

|          | 1 24-Hour                                                                                    |  |  |

|          | Bit 0 = Daylight Savings Time                                                                |  |  |

|          | 0 Disable<br>1 Enable                                                                        |  |  |

| 0Ch      | Status Register C                                                                            |  |  |

|          | Bit 7 = Interrupt Flag                                                                       |  |  |

|          | Bit 6 = Periodic Interrupt Flag                                                              |  |  |

|          | Bit 5 = Alarm Interrupt Flag                                                                 |  |  |

|          | Bit 4 = Update Interrupt Flag                                                                |  |  |

|          | Bits 3-0 = Reserved                                                                          |  |  |

| 0Dh      | Status Register D                                                                            |  |  |

|          | Bit 7 = Real Time Clock                                                                      |  |  |

|          | 0 Lost Power<br>1 Power                                                                      |  |  |

|          | 1 1 01101                                                                                    |  |  |

| Location | Description                                                       |  |  |

|----------|-------------------------------------------------------------------|--|--|

| 0Eh      | CMOS Location for Bad CMOS and Checksum Flags                     |  |  |

|          | bit 7 = Flag for CMOS Lost Power                                  |  |  |

|          | 0 = Power OK                                                      |  |  |

|          | 1 = Lost Power                                                    |  |  |

|          | bit 6 = Flag for CMOS checksum bad                                |  |  |

|          | 0 = Checksum is valid                                             |  |  |

|          | 1 = Checksum is bad                                               |  |  |

| 0Fh      | Shutdown Code                                                     |  |  |

| 10h      | Diskette Drives                                                   |  |  |

|          | bits 7-4 = Diskette Drive A                                       |  |  |

|          | 0000 = Not installed                                              |  |  |

|          | 0001 = Drive A = 360 K                                            |  |  |

|          | 0010 = Drive A = 1.2 MB                                           |  |  |

|          | 0011 = Drive A = 720 K                                            |  |  |

|          | 0100 = Drive A = 1.44 MB                                          |  |  |

|          | 0101 = Drive A = 2.88 MB                                          |  |  |

|          | bits 3-0 = Diskette Drive B                                       |  |  |

|          | 0000 = Not installed                                              |  |  |

|          | 0001 = Drive B = 360 K                                            |  |  |

|          | 0010 = Drive B = 1.2 MB<br>0011 = Drive B = 720 K                 |  |  |

|          | 0110 = Drive B = 720 K<br>0100 = Drive B = 1.44 MB                |  |  |

|          | 0100 = Drive B = 1.44 MB                                          |  |  |

| 11h      | Reserved                                                          |  |  |

| 12h      | Fixed (Hard) Drives                                               |  |  |

|          | bits 7-4 = Hard Drive 0, AT Type                                  |  |  |

|          | 0000 = Not installed                                              |  |  |

|          | 0001-1110 Types 1 - 14                                            |  |  |

|          | 1111 = Extended drive types                                       |  |  |

|          | 16-44. See location 19h.                                          |  |  |

|          | bits 3-0 = Hard Drive 1, AT Type                                  |  |  |

|          | 0000 = Not installed                                              |  |  |

|          | 0001-1110 Types 1 - 14                                            |  |  |

|          | 1111 = Extended drive types 16-44.                                |  |  |

|          | See location 2Ah.                                                 |  |  |

|          | See the Fixed Drive Type Parameters Table in Chapter 2 for infor- |  |  |

|          | mation on drive types 16-44.                                      |  |  |

| 13h      | Reserved                                                          |  |  |

| Location | Description                                                                                         |  |  |

|----------|-----------------------------------------------------------------------------------------------------|--|--|

| 14h      | Equipment                                                                                           |  |  |

|          | bits 7-6 = Number of Diskette Drives                                                                |  |  |

|          | 00 = One diskette drive                                                                             |  |  |

|          | 01 = Two diskette drives                                                                            |  |  |

|          | 10, 11 = Reserved                                                                                   |  |  |

|          | bits 5-4 = Primary Display Type                                                                     |  |  |

|          | 00 = Adapter with option ROM                                                                        |  |  |

|          | 01 = CGA in 40 column mode<br>10 = CGA in 80 column mode                                            |  |  |

|          | 11 = Monochrome                                                                                     |  |  |

|          | bits 3-2 = Reserved                                                                                 |  |  |

|          | bit 1 = Math Coprocessor Presence                                                                   |  |  |

|          | 0 = Not installed                                                                                   |  |  |

|          | 1 = Installed                                                                                       |  |  |

|          | bit 0 = Bootable Diskette Drive                                                                     |  |  |

|          | 0 = Not installed                                                                                   |  |  |

|          | 1 = Installed                                                                                       |  |  |

| 15h      | Base Memory Size (in KB) - Low Byte                                                                 |  |  |

| 16h      | Base Memory Size (in KB) - High Byte                                                                |  |  |

| 17h      | Extended Memory Size in (KB) - Low Byte                                                             |  |  |

| 18h      | Extended Memory Size (in KB) - High Byte                                                            |  |  |

| 19h      | Extended Drive Type - Hard Drive 0                                                                  |  |  |

|          | See the <i>Fixed Drive Type Parameters Table</i> in Chapter 2 for information on drive types 16-44. |  |  |

| 1Ah      | Extended Drive Type - Hard Drive 1                                                                  |  |  |

|          | See the Fixed Drive Type Parameters Table in Chapter 2 for information on drive types 16-44.        |  |  |

| 1Bh      | Custom and Fixed (Hard) Drive Flags                                                                 |  |  |

|          | bits 7-6 = Reserved                                                                                 |  |  |

|          | bit 5 = Internal Floppy Diskette Controller                                                         |  |  |

|          | 0 = Disabled                                                                                        |  |  |

|          | 1 = Enabled                                                                                         |  |  |

|          | bit 4 = Internal IDE Controller                                                                     |  |  |

|          | 0 = Disabled                                                                                        |  |  |

|          | 1 = Enabled                                                                                         |  |  |

|          | bit 3 = Hard Drive 0 Custom Flag<br>0 = Disable                                                     |  |  |

|          | 1 = Enabled                                                                                         |  |  |

|          | bit 2 = Hard Drive 0 IDE Flag                                                                       |  |  |

|          | 0 = Disable                                                                                         |  |  |

|          | 1 = Enabled                                                                                         |  |  |

|          | bit 1 = Hard Drive 1 Custom Flag                                                                    |  |  |

|          | 0 = Disable<br>1 = Enabled                                                                          |  |  |

|          | bit 0 = Hard Drive 1 IDE Flag                                                                       |  |  |

|          | 0 = Disable                                                                                         |  |  |

|          | 1 = Enabled                                                                                         |  |  |

| Location  | Description                                                                                     |  |  |

|-----------|-------------------------------------------------------------------------------------------------|--|--|

| 1Ch       | Reserved                                                                                        |  |  |

| 1Dh       | EMS Memory Size Low Byte                                                                        |  |  |

| 1Eh       | EMS Memory Size High Byte                                                                       |  |  |

| 1Fh - 24h | Custom Drive Table 0                                                                            |  |  |

|           | These 6 bytes (48 bits) contain the following data:                                             |  |  |

|           | Cylinders Landing Zone 10 bits Write Precomp 10 bits Heads Sectors/Track 8 bits                 |  |  |

| 451       | Byte 0                                                                                          |  |  |

| 1Fh       | bits 7-0 = Lower 8 Bits of Cylinders                                                            |  |  |

| 20h       | Byte 1 bits 7-2 = Lower 6 Bits of Landing Zone bits 1-0 = Upper 2 Bits of Cylinders             |  |  |

| 21h       | Byte 2 bits 7-4 = Lower 4 Bits of Write Precompensation bits 3-0 = Upper 4 Bits of Landing Zone |  |  |

| 22h       | Byte 3 bits 7-6 = Reserved bits 5-0 = Upper 6 Bits of Write Precompensation                     |  |  |

| 23h       | Byte 4 bits 7-0 = Number of Heads                                                               |  |  |

| 24h       | Byte 5<br>bits 7-0 = Sectors Per Track                                                          |  |  |

| 25h - 2Ah | Custom Drive Table 1 These 6 bytes (48 bits) contain the following data:                        |  |  |

|           | Cylinders Landing Zone 10 bits Write Precomp 10 bits Heads Sectors/Track 8 bits                 |  |  |

| 25h       | Byte 0 bits 7-0 = Lower 8 Bits of Cylinders                                                     |  |  |

| 26h       | Byte 1 bits 7-2 = Lower 6 Bits of Landing Zone bits 1-0 = Upper 2 Bits of Cylinders             |  |  |

| 27h       | Byte 2 bits 7-4 = Lower 4 Bits of Write Precompensation bits 3-0 = Upper 4 Bits of Landing Zone |  |  |

| Location                | Description                                                                                                                                                                                                |  |  |

|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 28h                     | Byte 3 bits 7-6 = Reserved                                                                                                                                                                                 |  |  |

|                         | bits 5-0 = Upper 6 Bits of Write Precompensation                                                                                                                                                           |  |  |

|                         | Byte 4                                                                                                                                                                                                     |  |  |

| 29h                     | bits 7-0 = Number of Heads                                                                                                                                                                                 |  |  |

| 246                     | Byte 5                                                                                                                                                                                                     |  |  |

| 2Ah                     | bits 7-0 = Sectors Per Track                                                                                                                                                                               |  |  |

| 2Bh                     | Boot Password bit 7 = Enable/Disable Password 0 = Disable Password                                                                                                                                         |  |  |

|                         | 1 = Enable Password bits 6-0 = Calculated Password                                                                                                                                                         |  |  |

| 2Ch                     | SCU Password                                                                                                                                                                                               |  |  |

|                         | bit 7 = Enable/Disable Password                                                                                                                                                                            |  |  |

|                         | 0 = Disable Password<br>1 = Enable Password                                                                                                                                                                |  |  |

|                         | bits 6-0 = Calculated Password                                                                                                                                                                             |  |  |

| 2Dh                     | Reserved                                                                                                                                                                                                   |  |  |

| 2Eh                     | High Byte of Checksum - Locations 10h to 2Dh                                                                                                                                                               |  |  |

| 2Fh                     | Low Byte of Checksum - Locations 10h to 2Dh                                                                                                                                                                |  |  |

| 30h                     | Extended RAM (KB) detected by POST - Low Byte                                                                                                                                                              |  |  |

| 31h                     | Extended RAM (KB) detected by POST - High Byte                                                                                                                                                             |  |  |

| 32h                     | BCD Value for Century                                                                                                                                                                                      |  |  |

| 33h                     | Base Memory Installed                                                                                                                                                                                      |  |  |

|                         | bit 7 = Flag for Memory Size                                                                                                                                                                               |  |  |

|                         | 0 = 640KB<br>1 = 512KB                                                                                                                                                                                     |  |  |

|                         | bits 6-0 = Reserved                                                                                                                                                                                        |  |  |

| 34h                     | Minor CPU Revision                                                                                                                                                                                         |  |  |

|                         | Differentiates CPUs within a CPU type (i.e., 486SX vs 486 DX, vs 486 DX/2). This is crucial for correctly determining CPU input clock frequency. During a power on reset, Reg DL holds minor CPU revision. |  |  |

| 35h                     | Major CPU Revision                                                                                                                                                                                         |  |  |

|                         | Differentiates between different CPUs (i.e., 386, 486, Pentium). This is crucial for correctly determining CPU input clock frequency. During a power on reset, Reg DH holds major CPU revision.            |  |  |

| 36h                     | Hotkey Usage                                                                                                                                                                                               |  |  |

|                         | bits 7-6 = Reserved                                                                                                                                                                                        |  |  |

|                         | bit 5 = Semaphore for Completed POST bit 4 = Semaphore for 0 Volt POST (not currently used)                                                                                                                |  |  |

|                         | bit 3 = Semaphore for already in SCU menu                                                                                                                                                                  |  |  |

|                         | bit 2 = Semaphore for already in PM menu                                                                                                                                                                   |  |  |

|                         | bit 1 = Semaphore for SCU menu call pending bit 0 = Semaphore for PM menu call pending                                                                                                                     |  |  |

| 40h-7Fh                 | Definitions for these locations vary depending on the chipset.                                                                                                                                             |  |  |

| <del>-1</del> 011-71111 | Bommaono foi tricoc locationo vary depending on the dilipoet.                                                                                                                                              |  |  |

#### 3.4.1 <u>Harddisk PIO Modes</u>

**Block Mode Transfer:**

(Multi-Sector)

Block mode boots IDE drive performance by increasing the amount of data transferred.

No Block Mode: 512 Byte per interrupt

Block Mode: up to 64 kByte per interrupt

**LBA Mode:**

LBA (logical block addressing) is a new method of addressing data on a disk drive. In the standard ST506 (MFM) ISA hard disk, data is accessed via a cylinder - head - sector format.

LBA Mode disabled: max. 528 MByte per Disk

LBA Mode enabled: max. 8 Gbyte per Disk

**Attention:**

The BIOS enables the LBA Mode only, if the harddisk was formatted on a system with enabled LBA. If the drive (capacity > 528MB) is formatted on a system with disabled LBA, the PHOENIX BIOS will never enable

the LBA mode!

The maximum parameters are: 1024 Cyl., 16 heads, 63 Sec/Track

32Bit Transfer:

Some operating system can handle two 16Bit word as one 32Bit access. This accelerates the IDE transfer.

**Advanced PIO Modes:**

| F    | PIO-Mode: | Timing: | Transferspeed: | Remarks:       |

|------|-----------|---------|----------------|----------------|

| IDE  | 0         | 600ns   | 2 MByte/sec    | Slowest I/O    |

| IDE  | 1         | 383ns   | 5.5MByte/sec   | Standard I/O   |

| EIDE | 2         | 240ns   | 8.3MByte/sec   | Fast I/O, Mem. |

| EIDE | 3         | 180ns   | 11,3MByte/sec  | IORDY Protocol |

| EIDE | 4         | 120ns   | 16,6MByte/sec  | IORDY Protocol |

| EIDE | DMA 1     | 160ns   | 13,3MByte/sec  | DRQ, ATA-2     |

|      |           |         |                |                |

Warning:

Always begin with the PIO-Mode 0 in the manual mode (not autodetect) to test a new drive or if you have troubles in the automatic mode.

The autodetect mode of some drives select wrong PIO modes.

## 3.5 EEPROM saved CMOS Setup

The EEPROM has different functions, as listed below:

- Backup of the CMOS-Setup values.

- Storing system informations like: version, production date, customisation of the board, CPU type.

- · Storing user/application values.

The EEPROM will be updated automatically after exiting the BIOS setup menu. The system will operate also without any CMOS battery. While booting up, the CMOS is automatically updated with the EEPROM values.

If the system hangs or a problem appears, the following steps must be performed:

- 1. Reset the CMOS-Setup (use the jumper to reset or disconnect the battery for at least 10 minutes).

- 2. Press Esc until the system starts up.

- 3. Enter the BIOS Setup:

- a) load DEFAULT values

- b) enter the settings for the environment

- c) exit the setup

- 4. Restart the system.

- The user may access the EEPROM through the INT15 special functions. Refer to the chapter SFI functions 3.10.1.

- The system information are read only information. To read, use the SFI functions.

#### 3.6 Download the VGA-BIOS and the CORE-BIOS

#### Before downloading a BIOS, please check as follows:

- Select the SHADOW option in the BIOS, for a BIOS and VGA (if this option is available).

- Disable the EMM386 or other memory managers in the CONFIG.SYS of your bootdisk.

- Make sure, that the DOWN\_xxx.EXE programm and the BIOS to download are on the same path and directory!

- Boot the DOS without config.sys & autoexec.bat -> press "F5" while starting DOS boot.

- Is the empty diskspace, where the down.exe is located, larger than 64kB (for safe storage)

- Is the floppydisk not write-protected

#### Start the DOWNLOADING Tool with:

- Start the corresponding download tool. Refer to the table to see which tool fits in, each productgroup has its own download tool. Do never use the wrong one!

| Product:        | BIOS-Core download | VGA-BIOS download        | BIOS-Ext. download |

|-----------------|--------------------|--------------------------|--------------------|

| File-Extension: | *.COR              | *.V40 , *.V45 *.V48      | *.BIN              |

|                 |                    | depending on the product |                    |

| BIOS Size:      | 128k               | 32k                      | 32k                |

| Addressrange:   | E0000 - FFFFFh     | C0000 – C7FFFh           | C8000 - CFFFFh     |

|                 |                    |                          |                    |

| MSM386SN        | DOWN_3SN.EXE       | -                        | -                  |

| MSM386SV        | DOWN_3SV.EXE       | DOWN_3SV.EXE             | DOWN_3SV.EXE       |

| MSM486SL        | DOWN_4SN.EXE       | -                        | -                  |

| MSM486SN        | DOWN_4SN.EXE       | -                        | -                  |

| MSM486SV        | DOWN_4SV.EXE       | DOWN_4SV.EXE             | DOWN_4SV.EXE       |

| MSM486SE / SEV  | DOWN_4SE.EXE       | DOWN_4SE.EXE             | -                  |

| MSM486DN        | DOWN_4DX.EXE       | -                        | -                  |

| MSM486DX        | DOWN_4DX.EXE       | DOWN_4DX.EXE             | DOWN_4DX.EXE       |

| SM-486PC / EK   | DOWN SM4.EXE       | On the –EK:              | <u>-</u>           |

|                 | _                  | DOWN_SM4.EXE             |                    |

| SM-486PCX / EK  | DOWN_S4X.EXE       | DOWN_S4X.EXE             | DOWN_S4X.EXE       |

| MSM5x86DX       | DOWN 4DX.EXE       | DOWN 4DX.EXE             | DOWN 4DX.EXE       |

| MSM-P5          | - AMI82602.EXE or  | DOWN 000.EXE             | -                  |

|                 | - FLASHAMI.COM     | _                        |                    |

|                 | (AMIBOOT.ROM)**    |                          |                    |

| PCC-P5L         | AMI82602.EXE       | DOWN_000.EXE             | -                  |

| PCC-PII         |                    |                          |                    |

| AMI- BIOS       |                    |                          |                    |

| PCC-P5L         | PHLASH.EXE         | DOWN_000.EXE             | -                  |

| PCC-PII         | PLATFORM.BIN       |                          |                    |

| PHOENIX- BIOS   |                    |                          |                    |

| MSM-P5S         | AMI82602.EXE       | DOWN_000.EXE             | -                  |