# Data Acquisition and Experiment Control

## **Missing References!!!**

Fixup ref to experience with TFC switch Ref to Conditions Database Reference to SPECS Reference to CC-PC

# **Technical Design Report**

Issue: Draft for Comment

Revision: 0.5

Reference: LHCb TDR xxx-2001 Created: 22-September 2001 Last modified: 22 November 2001 02:56

# The LHCb Collaboration

#### Brasilian Center for particles physics, CBPF, Rio de Janeiro, Brasil

P.R.Barbosa Marinho, I.Bediaga, A.F.Barbosa, G.Cernicchiaro, E.Correa de Oliveira, J.Magnin, J.Marques de Miranda, A.Massafferri, A.Reis, R.Silva

#### University of Rio de Janeiro, UFRJ, Rio de Janeiro, Brasil

S.Amato, P.Colrain, T.da Silva, J.R.T.de Mello Neto, L.de Paula, M.Gandelman, J.H.Lopes, B.Marechal, D.Moraes(1), E.Polycarpo, F.Vinci do Santos

(1) also at CERN

#### University of Clermont-Ferrand II, Clermont-Ferrand, France

Z.Ajaltouni, G.Bohner, V.Breton, R.Cornat, O.Deschamps, P.Henrard, J.Lecoq, P.Perret, C.Rimbault, C.Trouilleau<sup>1</sup>

#### CPPM Marseille, Aix University-Marseille II, Marseille, France

E.Aslanides, J.P.Cachemiche, P.Y.Duval, R.Le Gac, O.Leroy, P.L.Liotard, M.Menouni, R.Potheau, A.Tsaregorodtsev, B.Viaud

### University of Paris-Sud, LAL Orsay, Orsay, France

G.Barrand, C.Beigbeder-Beau, D.Breton, T.Caceres, O.Callot, Ph.Cros, B.D'Almagne, B.Delcourt, F.Fulda Quenzer, A.Jacholkowska<sup>2</sup>, B.Jean-Marie, J.Lefrançois, F.Machefert, V.Tocut, K.Truong

#### Technical University of Dresden, Dresden, Germany

R.Schwierz, B.Spaan

#### Max-Planck-Institute for Nuclear Physics, Heidelberg, Germany

C.Bauer, D.Baumeister, N.Bulian, H.P.Fuchs, T.Glebe, W.Hofmann, K.T.Knöpfle, S.Löchner, A.Ludwig, F.Sanchez Nieto, M.Schmelling, B.Schwingenheuer, E.Sexauer<sup>3</sup>, U.Trunk

#### Physics Institute, University of Heidelberg, Heidelberg, Germany

S.Bachmann, P.Bock, H.Deppe, F.Eisele, M.Feuerstack-Raible, S.Henneberger, P.Igo-Kemenes, R.Rusnyak, U.Stange, M.Walter, D.Wiedner, U.Uwer

#### Kirchhoff Institute for Physics, University of Heidelberg, Heidelberg, Germany

V.Lindenstruth, R.Richter, M.W.Schulz, A.Walsch

#### Laboratori Nazionali dell' INFN, Frascati, Italy

G.Bencivenni, C.Bloise, F.Bossi, P.Campana, G.Capon, P.DeSimone, C.Forti, M.A.Franceschi, F.Murtas, M.Palutan, L.Passalacqua, V.Patera(1), A. Sciubba(1)

(1) also at Dipartimento di Energetica, University of Rome, "La Sapienza"

#### University of Bologna and INFN, Bologna, Italy

M.Bargiotti, A.Bertin, M.Bruschi, M.Capponi, I.D'Antone, S.de Castro, P.Faccioli, L.Fabbri, D.Galli, B.Giacobbe, I.Lax, U.Marconi, I.Massa, M.Piccinini, M.Poli, N.Semprini-Cesari, R.Spighi, V.Vagnoni, S.Vecchi, M.Villa, A.Vitale, A.Zoccoli

#### University of Cagliari and INFN, Cagliari, Italy

S.Cadeddu, A.Cardini, M.Caria, A.Lai, D.Pinci, B.Saitta(1)

(1) also at CERN

#### University of Ferrara and INFN, Ferrara, Italy

V.Carassiti, A.Cotta Ramusino, P.Dalpiaz, A.Gianoli, M.Martini, F.Petrucci, M.Savrié

#### University of Florence and INFN, Florence, Italy

A.Bizzeti, M.Calvetti, G.Collazuol, E.Iacopini, M.Lenti, F.Martelli, G.Passaleva, M.Veltri

#### University of Genoa and INFN, Genoa, Italy

S.Cuneo, F.Fontanelli, V.Gracco, P.Musico, A.Petrolini, M.Sannino

#### University of Milano-Bicocca and INFN, Milano, Italy

M.Alemi, T.Bellunato(1), M.Calvi, C.Matteuzzi, M.Musy, P.Negri, M.Paganoni, C.Piazzoni (1) also at CERN

#### University of Rome, "La Sapienza" and INFN, Rome, Italy

G.Auriemma(1), V.Bocci, C.Bosio, D.Fidanza(1), A.Frenkel, K.Harrison, G.Martellotti, S.Martinez, G.Penso, S.Petraca, G.Pirozzi, R.Santacesaria, C.Satriano(1), A.Satta

(1) also at University of Basilicata, Potenza

#### University of Rome, "Tor Vergata" and INFN, Rome, Italy

G.Carboni(1), D.Domenici, G.Ganis, R.Messi, L.Pacciani, L.Paoluzi, E.Santovetti

(1) also at CERN

#### **NIKHEF, The Netherlands**

G.van Apeldoorn(1,3), N.van Bakel(1,2), T.S.Bauer(1,4), J.F.J. van den Brand(1,2), H.J.Bulten(1,2), C.Carloganu (1), M.Doets(1), R.van der Eijk(1), I.Gouz(1,5), D.Groep(1), V.Gromov(1), R.Hierck(1), L.Hommels(1), E.Jans(1), T.Ketel(1,2), S.Klous (1,2), B.Koene(1), M.Merk(1), F.Mul(2), M.Needham(1), H.Schuijlenburg(1), T.Sluijk(1), J.van Tilburg(1), H.de Vries(1), L.Wiggers(1), E.Zupan(1)

- (1) Foundation of Fundamental Research of Matter in the Netherlands

- (2) Free University Amsterdam

- (3) University of Amsterdam

- (4) University of Utrecht

#### Institute of High Energy Physics, Beijing, P.R.C.

C.Gao, C.Jiang, H.Sun, Z.Zhu

#### Research Centre of High Energy Physics, Tsinghua University, Beijing, P.R.C.

M.Bisset, J.P.Cheng, Y.G.Cui, Y.Dai, Y.Gao, H.J.He, C.Huang, Y.P.Kuang, Q.Li, Y.J.Li, Y.Liao, J.P.Ni, B.B.Shao, J.J.Su, Y.R.Tian, Q.Wang, Q.S.Yan

#### Institute for Nuclear Physics and University of Mining and Metalurgy, Krakow, Poland

E.Banas, J.Blocki, K.Galuszka, L.Hajduk, P.Jalocha, P.Kapusta, B.Kisielewski, W.Kucewicz, T.Lesiak, J.Michalowski, B.Muryn, Z.Natkaniec, W.Ostrowicz, G.Polok, E.Rulikowska-Zarebska, M.Stodulski, T.Szumlak, M.Witek(1), P.Zychowski

(1) also at CERN

#### Soltan Institute for Nuclear Physics, Warsaw, Poland

M.Adamus, A.Chlopik, Z.Guzik, A.Nawrot, M.Szczekowski

# Horia Hulubei-National Institute for Physics and Nuclear Engineering(IFIN-HH), Bucharest-Magurele, Romania

D.V.Anghel<sup>4</sup>, C.Coca, A.Cimpean, G.Giolu, C.Magureanu, S.Popescu(1), T.Preda, A.M.Rosca(2), V.L.Rusu<sup>5</sup>

- (1) also at CERN

- (2) also at Humbolt University, Berlin

#### Institute for Nuclear Research (INR), Moscow, Russia

V.Bolotov, S.Filippov, J.Gavrilov, E.Guschin, V.Kloubov, L.Kravchuk, S.Laptev, V.Laptev, V.Postoev, A.Sadovski, I.Semeniouk

#### Institute of Theoretical and Experimental Physics (ITEP), Moscow, Russia

S.Barsuk, I.Belyaev (1), A.Golutvin, O.Gouchtchine, V.Kiritchenko, V.Kochetkov, I.Korolko(1), G.Pakhlova, N.Levitski, A.Morozov, P.Pakhlov, D.Roussinov, V.Rusinov, S.Semenov, A.Soldatov, E.Tarkovski

(1) also at CERN

#### Budker Institute for Nuclear Physics (INP), Novosibirsk, Russia

K.Beloborodov, A.Bondar, A.Bozhenok, A.Buzulutskov, S.Eidelman, V.Golubev, P.Krokovnyi, S.Oreshkin, A.Poluektov, S.Serednyakov, L.Shekhtman, B.Shwartz, Z.Silagadze, A.Sokolov, A.Vasiljev

### Institute for High Energy Physics (IHEP-Serpukhov), Protvino, Russia

L.A.Afanassieva, I.V.Ajinenko, K.Beloous, V.Brekhovskikh, S.Denissov, A.V.Dorokhov, R.I.Dzhelyadin, A.Kobelev, A.K.Konoplyannikov, A.K.Likhoded, V.D.Matveev, V.Novikov, V.F.Obraztsov, A.P.Ostankov, V.I.Rykalin, V.K.Semenov, M.M.Shapkin, N.Smirnov, A.Sokolov, M.M.Soldatov, V.V.Talanov, O.P.Yushchenko

#### Petersburg Nuclear Physics Institute, Gatchina, St. Petersburg, Russia

B.Botchine, S.Guetz, A.Kashchuk(1), V.Lazarev, N.Saguidova, V.Souvorov(1), E.Spiridenkov, A.Vorobyov, An.Vorobyov

(1) also at CERN

#### University of Barcelona, Barcelona, Spain

E.Aguilo, R.Ballabriga(1), S.Ferragut, Ll.Garrido, D.Gascon, R.Graciani Diaz, S.Luengo(1), R.Miquel<sup>6</sup>, D.Peralta, M.Rosello(1), X.Vilasis(1)

(1) also at departament d'Engineria Electronica La Salle, Universitat Ramon Llull, Barcelona

### University of Santiago de Compostela, Santiago de Compostela, Spain

B.Adeva, P.Conde, F.Gomez, J.A.Hernando, A.Iglesias, A.Lopez-Aguera, A.Pazos, M.Plo, J.M.Rodriguez, J.J.Saborido, M.J.Tobar

#### University of Lausanne, Lausanne, Switzerland

P.Bartalini, A.Bay, B.Carron, C.Currat, O.Dormond, F.Dürrenmatt, Y.Ermoline, R.Frei, G.Gagliardi, G.Haefeli, J.P.Hertig, P.Koppenburg, T.Nakada(1), J.P.Perroud, F.Ronga, O.Schneider, L.Studer, M.Tareb, M.T.Tran

(1) also at CERN, on leave from PSI, Villigen

#### University of Zürich, Zürich, Switzerland

R.Bernet, E.Holzschuh, F.Lehner, P.Sievers, O.Steinkamp, U.Straumann, A.Vollhardt, D.Wyler, M.Ziegler

#### Institute of Physics and Technologies, Kharkiv, Ukraine

A.Dovbnya, S.Maznichenko, O.Omelaenko, Yu.Ranyuk, V.Shulayev

#### Institute for Nuclear Research, Kiev, Ukraine

V.Aushev, V.Kiva, I.Kolomiets, Yu.Pavlenko, V.Pugatch, Yu.Vasiliev

#### University of Bristol, Bristol, U.K.

N.H.Brook, J.E.Cole, R.D.Head, A.Phillips, A.Presland, F.F.Wilson

#### University of Cambridge, Cambridge, U.K.

K.George, V.Gibson, C.R.Jones, S.G.Katvars, C.Shepherd-Themistocleous, C.P.Ward, S.A.Wotton

#### Rutherford Appleton Laboratory, Chilton, U.K.

C.A.J.Brew<sup>7</sup>, C.J.Densham, S.Easo, B.Franek, J.G.V.Guy, R.N.J.Halsall, J.A.Lidbury, J.V.Morris, A.Papanestis, G.N.Patrick, F.J.P.Soler, S.A.Temple, M.L.Woodward

#### University of Edinburgh, Edinburgh, U.K.

A.Barczyk, S.Eisenhardt, A.Khan, F.Muheim, S.Playfer, A.Walker

### University of Glasgow, Glasgow, U.K.

A.J.Flavell, A.Halley, V.O'Shea, A.Pickford, F.J.P.Soler

### University of Liverpool, Liverpool, U.K.

S.Biagi, T.Bowcock, R.Gamet, M.McCubbin, J.Palacios, C.Parkes, G.Patel, V.Wright

#### Imperial College, London, U.K.

G.J.Barber, D.Clark, P.Dauncey, A.Duane, U.Egede, M.Girone(1), J.Hassard, R.Hill, M.J.John<sup>8</sup>, S.Jolly, D.R.Price, P.Savage, L.Toudup, D.Websdale

(1) also at CERN

#### University of Oxford, Oxford, U.K

M.Adinolfi, G.Damerell, J.H.Bibby, M.J.Charles, N.Harnew, F.Harris, I.A.McArthur, J.Rademacker, N.J.Smale, S.Topp-Jorgensen, G.Wilkinson

#### CERN, Geneva, Switzerland

G. Anelli, F.Anghinolfi, F.Bal, M.Benayoun(1), R. Beneyton<sup>9</sup>, W.Bonivento(2), A.Braem, J.Buytaert, M.Campbell, A.Cass, M.Cattaneo, Ph.Charpentier, E.Chesi, J.Christiansen, J.Closier, P.Collins, G.Corti, C.D'Ambrosio, H.Dijkstra, J.P.Dufey, M.Ferro-Luzzi, F.Fiedler, W.Flegel, F.Formenti, R.Forty, M.Frank, C.Frei, I.Garcia Alfonso, C.Gaspar, P.Gavillet, G.Gracia Abril<sup>10</sup>, A. Guirao Elias, T.Gys, F.Hahn, S.Haider, J.Harvey, B.Hay<sup>11</sup>, E.van Herwijnen, H.J.Hilke, G.von Holtey, D.Hutchroft, R.Jacobsson, P.Jarron, C.Joram, B.Jost, D.Lacarrère, M.Laub<sup>12</sup>, M.Letheren, J.F.Libby, C.Lippmann, R.Lindner, M.Losasso, P.Mato Vila, H.Müller, N.Neufeld, K.Osterberg, C.Padilla, U.Parzefall, S.Ponce, F.Ranjard, W.Riegler, F.Rohner, S.Roiser, T.Ruf, S.Schmeling, B.Schmidt, T.Schneider, A.Schopper, W.Snoeys, W.Tejessy, F.Teubert, J.Toledo Alarcon<sup>13</sup>, O.Ullaland, A.Valassi, P.Vazquez Regueiro, I.Videau, P.Wertelaers, A.Wright<sup>14</sup>, K.Wyllie

(1) on leave from Université de Paris VI et VII (LPNHE), Paris

(2) on leave from INFN Cagliari, Cagliari

# **Acknowledgements**

We would like to thank Manual Mazo and Konrad Paszkiewicz for the work they have done during their stay as summer students in 2001.

We would also like to acknowledge the CMS DAQ group for giving us access to their switching test-bed for studies in the context of the performance measurements of the Foundry switch.

<sup>&</sup>lt;sup>1</sup>now at Thales Microelectonics, Grenoble, France

<sup>&</sup>lt;sup>2</sup>now at Groupe d'Astroparticules de Montpellier (GAM), Montpellier, France

<sup>&</sup>lt;sup>3</sup>now at Dialog Semiconductor, Kirchheim-Nabern, Germany

<sup>&</sup>lt;sup>4</sup>now at Oslo University, Oslo, Norway

<sup>&</sup>lt;sup>5</sup>now at Pennsylvania University, Philadelphia, USA

<sup>&</sup>lt;sup>6</sup>now at LBNL, Berkeley, USA

<sup>&</sup>lt;sup>7</sup>now at Fermilab, Chicago, USA

<sup>&</sup>lt;sup>8</sup>now at Collège de France, Paris, France

<sup>&</sup>lt;sup>9</sup> Now at Université de Paris Sud, LAL-Orsay, Paris

<sup>&</sup>lt;sup>10</sup>now at ENWARE, Madrid, Spain

<sup>&</sup>lt;sup>11</sup>now at SWX Swiss Exchange, Geneva, Switzerland

<sup>&</sup>lt;sup>12</sup>now at Technical University of Prague, Prague, Czech Republic

<sup>&</sup>lt;sup>13</sup>now at Polytechnical University of Valencia, Valencia, Spain

<sup>&</sup>lt;sup>14</sup>now at Lancaster University, Lancaster, UK

# **Table of Contents**

| 1. | Intro | ductionduction                                | 1  |

|----|-------|-----------------------------------------------|----|

|    | 1.1   | Overview                                      | 1  |

|    |       | 1.1.1. Trigger / DAQ Overview                 | 2  |

|    |       | 1.1.2. Design and Implementation Goals        | 3  |

|    | 1.2   | Structure of the Document                     |    |

| 2. | Requ  | irements                                      | 5  |

|    | 2.1   | Physics Requirements                          | 6  |

|    | 2.2   | LHCb Detector                                 | 6  |

|    | 2.3   | LHCb Trigger System                           | 7  |

|    | 2.4   | LHC Accelerator                               | 8  |

|    | 2.5   | Data Processing and Offline Computing         | 8  |

|    | 2.6   | Experiment Operations                         | 9  |

|    | 2.7   | Running Modes and Partitioning                | 9  |

|    | 2.8   | Infrastructure Services                       | 10 |

|    | 2.9   | Summary of performance requirements           | 11 |

| 3. | Syste | m Design                                      | 12 |

|    | 3.1   | Design Goals                                  | 12 |

|    | 3.2   | System Architecture                           | 12 |

|    | 3.3   | Timing and Fast Controls                      | 14 |

|    |       | 3.3.1. TFC Architecture and Partitioning      | 14 |

|    |       | 3.3.2. TTC Distribution System                |    |

|    |       | 3.3.3. Readout Supervisor                     |    |

|    |       | 3.3.4. TFC Switch                             |    |

|    |       | 3.3.5. Throttle Switch and the Throttle OR    | 18 |

|    | 3.4   | Dataflow System                               |    |

|    |       | 3.4.1. Front-End Multiplexer Layer            | 19 |

|    |       | 3.4.2. Readout Unit Layer                     |    |

|    |       | 3.4.3. Readout Network Layer                  |    |

|    |       | 3.4.4. Sub-Farm Controller Layer              |    |

|    |       | 3.4.5. Data-Flow Protocol and Traffic Control |    |

|    | 3.5   | Event Filter Farm                             |    |

|    | 3.6   | Experiment Control System                     |    |

|    |       | 3.6.1. ECS Architecture                       |    |

|    |       | 3.6.2. ECS Design Concepts and Guidelines     |    |

|    | 3.7   | Summary of Key Features                       |    |

| 4. | •     | m Implementation                              |    |

|    | 4.1   | Timing and Fast Controls                      |    |

|    |       | 4.1.1. TTC Distribution System                |    |

|    |       | 4.1.2. Readout Supervisor                     |    |

|    |       | 4.1.3. Realisation of the Readout Supervisor  |    |

|    |       | 4.1.4. TFC Switch                             |    |

|    |       | 4.1.5. Throttle Switch and Throttle OR        |    |

|    | 4.2   | Data Link Technology and Link Protocols       |    |

|    | 4.3   | Front-End Multiplexing and Readout Units      |    |

|    |       | 4.3.1. R&D Activities                         |    |

|    |       | 4.3.2. FPGA-Based FEM/RU                      |    |

|    |       | 4.3.3. Network Processor-Based FEM/RU         | 38 |

|                 | 4.3.4. Baseline Implementation                   |    |

|-----------------|--------------------------------------------------|----|

| 4.4             | $\boldsymbol{c}$                                 |    |

|                 | 4.4.1. Solutions Based on Commercial Switches    |    |

|                 | 4.4.2. Solutions based on Network Processors     |    |

| 4.5             |                                                  |    |

| 4.6             | 1                                                |    |

|                 | 4.6.1. Control Framework and Tools               |    |

|                 | 4.6.2. Data Acquisition Control                  |    |

|                 | 4.6.3. Detector Control                          |    |

|                 | 4.6.4. Infrastructure Control                    |    |

|                 | 4.6.5. Detector Safety System                    |    |

|                 | 4.6.6. Data Processing and Offline Computing     | 63 |

| 4.7             |                                                  |    |

|                 | 4.7.1. Timing and Fast Control                   | 64 |

|                 | 4.7.2. Data-Flow System                          | 64 |

|                 | 4.7.3. Event Filter Farm                         | 66 |

|                 | 4.7.4. ECS                                       | 66 |

| 4.8             | Online Computing Infrastructure                  | 69 |

|                 | 4.8.1. Computing and Network Infrastructure      | 69 |

|                 | 4.8.2. Power and Cooling                         |    |

|                 | 4.8.3. Location of Equipment                     |    |

|                 | 4.8.4. Control Room                              |    |

|                 | 4.8.5. Connection to the CERN Computer Centre    |    |

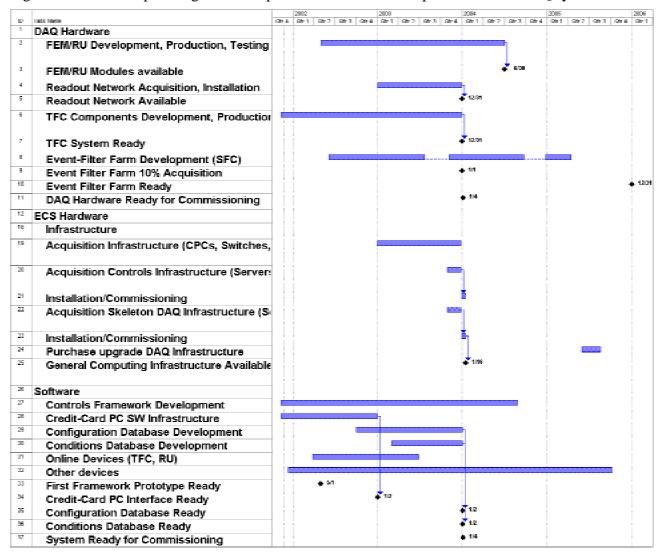

| 5. Cos          | st, Planning and Responsibilities                |    |

| 5.1             | Costing                                          |    |

| 5.2             | C                                                |    |

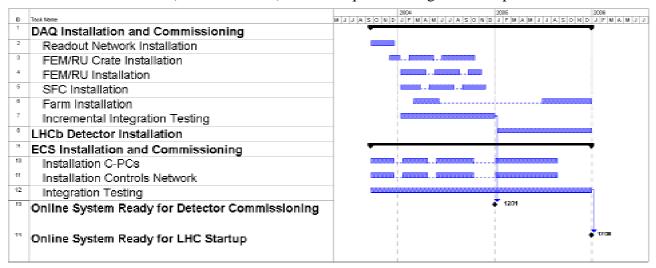

| 3.2             | 5.2.1. Implementation Phase                      |    |

|                 | 5.2.2. Integration and Commissioning Phase       |    |

| 5.3             |                                                  |    |

| 3.3             | 5.3.1. Software                                  |    |

|                 | 5.3.2. Hardware                                  |    |

| Annandiv        | A Event-Building R&D Studies                     |    |

| Appendix<br>A.1 | 6                                                |    |

| A.1<br>A.2      | J                                                |    |

| A.2<br>A.3      | $\epsilon$                                       |    |

|                 |                                                  |    |

| A.4             | 1 23                                             |    |

|                 | A.4.1 Load                                       |    |

|                 | A.4.2 Switching Strategies                       |    |

|                 | A.4.3 Traffic Shaping                            |    |

| A 1'            | A.4.4 Transport Protocols and Safe Data Transfer |    |

| Appendix        |                                                  |    |

|                 | E LHCb Testbeam Computing Setup                  |    |

| PV              | SS Control for CASCADE Stages                    |    |

|                 | Second Step                                      |    |

|                 | Central Data Recording                           |    |

|                 | User Information and Interactive System Support  |    |

|                 | Experience in 2001                               |    |

|                 | es                                               |    |

| Glossary        | of Terms                                         | 99 |

# 1. Introduction

### 1.1 Overview

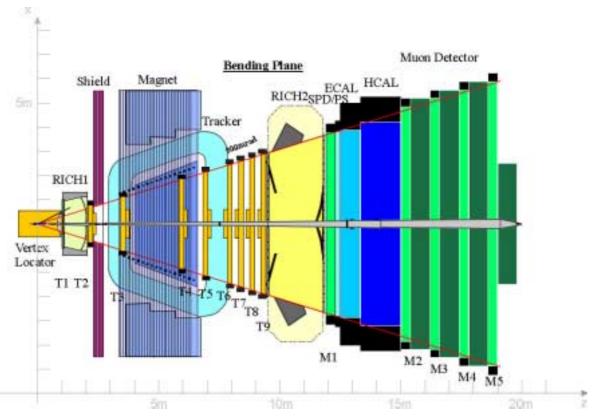

The LHCb detector is designed to exploit the large number of b-hadrons produced at the LHC in order to make precision studies of CP asymmetries and of rare decays in the B-meson systems. LHCb is a single-arm spectrometer with a forward angular coverage from 10 mrad to 300 mrad in the horizontal projection and to 250 mrad in the vertical projection. The layout of the spectrometer is shown in Figure 1. The detector can reconstruct a B-decay vertex with very good resolution and provides excellent particle identification for charged particles. It has a high performance trigger, which is optimised to select events with B-mesons efficiently, based on particles with large transverse momentum and displaced secondary vertices.

Figure 1 Schematic drawing of the LHCb detector as seen from above.

LHCb comprises a number of different sub-detectors:

- The Vertex Locator (VELO) features a series of silicon stations placed along the beam direction and is used to provide precise measurements of track coordinates close to the interaction region. These are used to reconstruct production and decay vertices of beauty and charm hadrons, to provide an accurate measurement of their lifetimes, and to measure the impact parameter of particles used to tag their flavour.

- Charged particle identification is achieved through two Ring Image Cherenkov Counters, an upstream detector (RICH1) containing aerogel and C<sub>4</sub>F<sub>10</sub> radiators and a downstream detector (RICH2) having a CF<sub>4</sub> radiator. Three radiators are used in order to cover the full momentum range.

1 Introduction Page 1

- The calorimeter system comprises a scintillator pad detector (SPD), a preshower detector (PS) and an electromagnetic calorimeter (ECAL) followed by a hadron calorimeter (HCAL). Together they provide high transverse energy hadron, electron and photon candidates for the Level 0 trigger, identification of electrons for flavour tagging and good reconstruction of  $\pi^0$ s and photons for study of B-meson decays.

- A spectrometer dipole magnet, which is placed close to the interaction region in order to minimise its size.

- The tracking system consists of a series of stations with Inner (IT) and Outer (OT) components for finding particle tracks in the region between the vertex detector and the calorimeters and for measuring particle momenta.

- The muon detector (MUON) uses the penetrative power of muons to provide a robust muon trigger.

LHCb plans to operate with an average luminosity of  $2 \times 10^{32} \text{ cm}^{-2} \text{ s}^{-1}$ , which should be obtained from the beginning of LHC operation. About  $10^{12} \ b\overline{b}$  pairs are expected to be produced in one year of running which corresponds to a production rate of ~75 kHz. However, events with fully reconstructed interesting  $b\overline{b}$  final states represent only a small fraction of the total  $b\overline{b}$  sample due to the small branching ratios and limited detector acceptance. The LHCb trigger system will select the small fraction of interesting events from the large number of  $b\overline{b}$  and other pp inelastic events.

The first two levels of trigger will be applied whilst data from the detectors are still buffered in the front-end electronics. The role of the data acquisition system (DAQ) is to collect zero suppressed data corresponding to triggered events and to assemble them into complete events. It must also filter and fully reconstruct interesting events, using high level trigger algorithms running in a powerful CPU farm, and dispatch them to permanent storage. The Experiment Control System (ECS) will be used to configure the readout system, to control and monitor the state of the detector components, to steer the actual data taking and to provide checks of the quality of the data recorded for physics analysis.

In the following, we first give an overview on the architecture of the trigger and data acquisition systems, followed by a discussion of the design and implementation goals. We then describe how the design and implementation of each component is covered in the body of this Technical Design Report (TDR).

#### 1.1.1. Trigger / DAQ Overview

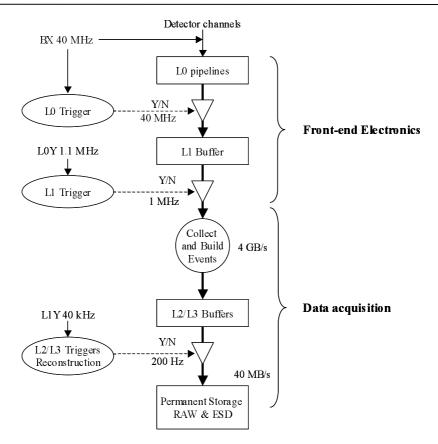

Data flows through the various stages of the DAQ system under the control of a four level trigger system (Figure 2). Level 0 is a high p<sub>T</sub> trigger operating at the bunch crossing frequency of 40 MHz, and is designed to achieve a total suppression factor of ~40. It has a fixed latency of 4 µs and is distributed to the front-end pipelines in a time-synchronised manner. Level 1 uses the VELO to select events containing one or more secondary vertices. It operates at the Level 0 accept rate, nominally 1 MHz, and has a suppression factor of 25. The Level 1 trigger is also distributed to the front-end electronics. The transfer of data from the front-end electronics to the DAQ system is initiated by a positive Level 1 decision, which runs at 40 kHz. The average event length of these zero-suppressed data is 100 kB and thus the task of the DAQ is to assemble complete events at a total rate of 4 GB/s. The high level triggers (Level 2 and Level 3) comprise sophisticated software algorithms working on complete events. They implement a number of selection criteria that are successively applied reducing the overall rate of accepted events to a nominal 200 Hz. These events are reconstructed promptly online and the output of the reconstruction, Event Summary Data (ESD), is written to permanent storage together with the data collected from the detectors (RAW).

Page 2 1 Introduction

Figure 2 Schematic diagram of the LHCb trigger and data acquisition system

### 1.1.2. Design and Implementation Goals

Our approach to the design and implementation of the LHCb DAQ and ECS systems has been strongly influenced by our experience building and operating the ALEPH and DELPHI systems at LEP [1], [2]. We have found that the ability to maintain very high running efficiencies, to adapt the system to changing needs and to operate under special running modes is strongly influenced by the way the system is originally conceived and specified. A cohesive online team working closely together and with strong links to sub-detector groups is also considered to be an important ingredient for the success of the project.

For LHCb special attention has been placed on specification of the system architecture, of the dataflow protocols and of the main functional elements. These specifications are independent of the particular implementation choice, thus permitting upgrades to be made later on that can take advantage of new technologies without requiring change to the underlying architecture. Baring in mind the extreme data rates (4 GB/s) and the large number of readout elements and links needed to realise the system, a guiding principle has been to keep the design as simple as possible in order to ensure safe and reliable operation. For example, event fragments are routed through the Readout Network to form full events in the destination CPUs without the need of a central flow control unit. This considerably simplifies the dataflow protocol and minimises the number of different functional units that have to be designed and built. In addition, complete events are immediately made available, permitting full flexibility in defining and applying the high-level trigger algorithms. The architecture has also been developed with careful attention to its scalability in order to be able to cope with larger data rates and processing power should this be required in the future.

It has also been a requirement that each sub-detector group should be given some autonomy in the operation of the readout of their hardware and therefore a key feature of the readout architecture is

1 Introduction page 3

the concept of 'partitioning'. Partitioning is needed in order to support parallel and independent data-taking activities, which will be needed during the commissioning of the system and especially for making calibrations and tests outside of normal data-taking periods. As the name suggests, pieces of the readout system can be partitioned electronically so as to create autonomous data acquisition subsystems. A partition is therefore defined as being any section of the readout system that can be configured to function independently of the rest of the system. Each partition consists of a 'pipeline' in which data flows from the front-end electronics to a subset of the CPUs executing the final software algorithms. Examples of these are the trigger, reconstruction or calibration tasks, depending on the activity in progress. More than one partition may exist at any one time thus permitting parallel data streams. Support of partitioning has particularly important consequences for the design of the system used to distribute the timing and trigger decisions to the front-end electronics.

Wherever possible we have chosen to standardise on common components, to minimise the effort needed to develop the system and to ease maintenance in the long term. Thus there are no LHCb sub-detector-specific implementations of standard readout elements. In addition we also make use of common LHC developments, such as the Trigger Timing and Control (TTC) distribution system [2], and are following more recent efforts in CERN/EP division to specify crates and rack control systems. We also intend to participate in projects organised in CERN/IT division concerning the management of large scale computing fabrics for deployment in CPU farms. Finally, we use the latest state-of-the-art commercial components for their programmability, and hence the extra flexibility they afford us.

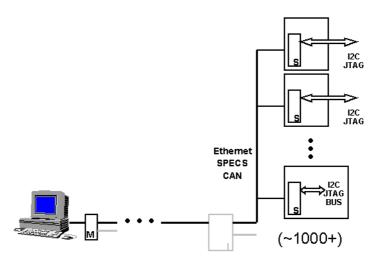

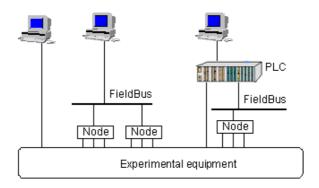

A dedicated local area network will be used to provide a communication and control path between the main online computers and each component of the readout system. This control path is used to configure, control and monitor the various elements of the system and is physically completely separate from the path used to collect the data. Provision of a secure and independent communication path to each hardware module is considered to be essential for detecting and recovering from errors in the readout system. This path will also be used by the ECS to acquire slowly changing data from the detector to keep a permanent record of environmental parameters (temperatures, gas pressures etc.).

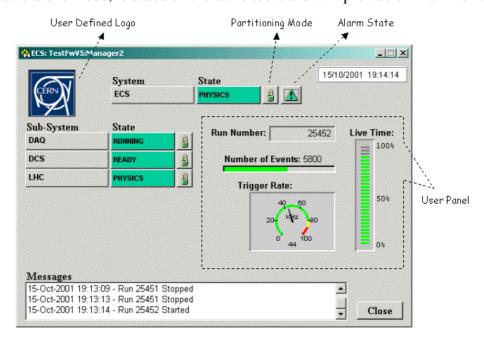

A common software framework is under development in the context of the Joint Controls Project [4], in which LHCb team members are actively participating. This framework also makes use of a commercial software package [4], which has considerably eased the development of the large set of control and monitoring applications constituting the online system. The existing software infrastructure provides a very good paradigm for communication between developers from all subdetector groups, as well as between developers on different experiments. It should permit the development of a very coherent interface for the shift crew, which should simplify the task of running the system, identifying problems and recovering from them.

#### 1.2 Structure of the Document

This Technical Design Report is designed to be a concise but self-contained description of the LHCb data acquisition and experiment control systems. Further technical details can be found in a number of supporting technical notes that are referenced in the body of the text. In Chapter 2 we describe the environment in which the system operates and the requirements placed on it by the physics programme, the LHC collider and the LHCb detector itself. Chapter 3 outlines the design of the architecture and identifies the main functional elements. Chapter 4 describes the detailed implementation of the system, mentioning technology choices. The TDR concludes in Chapter 5 with a discussion of the cost, planning and assignment of responsibilities.

Page 4 1 Introduction

# 2. Requirements

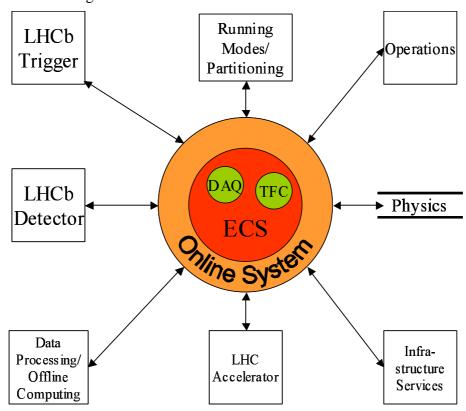

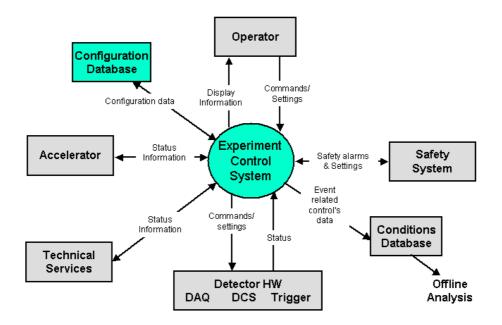

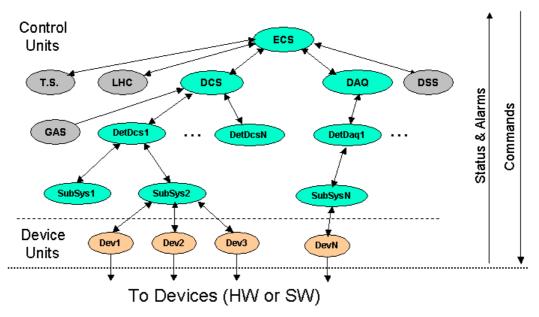

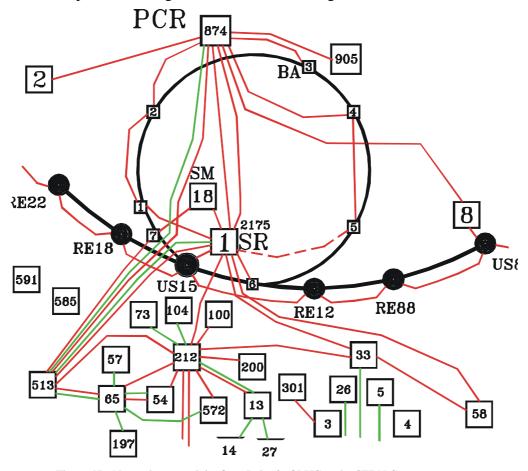

The environment in which the online system must operate is represented in the form of a Context Diagram in Figure 3. This shows all the external components with which the online system must interact and which form a useful basis for classifying all the requirements placed on the system. In making the design for the realisation of the DAQ/ECS system, careful consideration has been given to satisfying all these requirements, as well as satisfying the need to operate within the technological and financial constraints and to choose an approach that will match the expertise of the LHCb online team.

It is evident that the DAQ/ECS system must provide facilities for collecting data from the detector and for configuring and supervising the operation of the detector. However there is a wide spectrum of requirements that come from the need to communicate with other systems. For example, the data bandwidths that must be sustained by the DAQ are largely determined by the performance of the trigger system. Many requirements on the system come from operational issues, such as the need to support various running modes (tests, calibrations, normal running) and partitioning. As is evident in a colliding beam machine, the operation of the experiments and the LHC accelerator are tightly coupled and communication of control and status information between the two is required at hardware and software levels. The environment in the experimental area must be monitored to ensure the correct operation of basic services, such as ventilation and cooling, and to satisfy safety criteria. A fundamental goal is to satisfy the needs of the physics programme. All these areas provide input on the functionality and performance required of the system and are discussed in more detail in the following sections.

Figure 3 Context diagram showing components in which the LHCb online system will run.

2 Requirements page 5

# 2.1 Physics Requirements

LHCb is an experiment dedicated to the study of CP violation in hadronic systems originating from b-quarks. These effects can only be observed in tiny asymmetries in the distribution of some observables when comparing B and  $\overline{B}$  - mesons. The effective fraction of interesting events is very small (of the order of  $10^{-5}$  or less). Hence, despite the fact that with an LHC luminosity of  $2.10^{32}$  more than 100 thousand B mesons are produced each second, only a very small fraction of these are selected and stored for further analysis offline. It is therefore of the utmost importance to design and implement as efficient a trigger as possible. The counterpart is that this can only be achieved at the price of a relatively high level of background originating mainly from non-interesting B decays, inducing a high demand on the capabilities of the readout system. Clearly, reliability and efficiency are expected from the online system in order to record as many interesting events as possible.

### 2.2 LHCb Detector

Ten sub-detectors and two-levels of triggering contribute data that must be collected by the DAQ for each triggered event. The channel count corresponding to these components varies between a few hundred (trigger systems) and several hundred thousands (the tracker system), totalling approximately 1.1 Million for the complete detector (Table 1). The average total event size has been estimated from average detector occupancies, determined through simulation studies, to be ~80 kB. An average event size of 100 kB has therefore been assumed for the purposes of calculating the bandwidth that must be sustained by the DAQ. An additional requirement is that the readout system must be able to accept very large events (several MB) carrying calibration data.

|                               | VELO | RICH1 | RICH2 | IT  | ОТ  | SPD | PS | ECAL | HCAL | Muon | TRIG |

|-------------------------------|------|-------|-------|-----|-----|-----|----|------|------|------|------|

| Number of<br>Channels [k]     | 205  | 172   | 278   | 220 | 120 | 6   | 6  | 6    | 1.5  | 120  | 1    |

| Average<br>Occupancy<br>[%]   | 0.7  | 1     | 1     | 1.3 | 10  | 7   | 7  | 7    | 13   | 1.5  | -    |

| Maximum<br>Occupancy<br>[%]   | 1.5  | 8     | 3     | 5   | 25  | 20  | 20 | 18   | 57   | 5    | -    |

| Average<br>Event Size<br>[kB] | 5    | 6     | 10    | 10  | 33  | 3   | 3  | 4    | 2    | 2    | 1    |

Table 1 LHCB DETECTOR CHANNELS, OCCUPANCIES AND AVERAGE EVENT SIZES

The LHCb online system must ensure the safe and efficient recording of physics data from the LHCb detector. The data acquisition system must ensure the error-free<sup>1</sup> transmission of the data from the front-end electronics to the storage device. This transfer of data should not introduce deadtime, if the system is operated within the design parameters. The online system will also be responsible for setting-up and monitoring the equipment involved in the data acquisition, in particular the sub-detector front-end electronics.

Page 6 2 Requirements

<sup>&</sup>lt;sup>1</sup> Of course, there is never a data transfer system that operates error free. If errors occur, however, they should be detected and the corresponding data should be flagged as error prone.

A potential upgrade to achieve higher data throughputs, e.g. due to larger event sizes and/or higher trigger rates, must be envisaged. It should be possible to achieve this through a simple rescaling of the size of the readout system, i.e. by adding readout modules, and not by changing the architecture of the system i.e. by introducing new functional elements or protocols.

Since the number of readout modules is large, the functionality of each type of module and the protocols that govern the data transfer should be as simple and reliable as possible. This will help to keep the mean time between failures to a maximum, will simplify the procedure of locating and fixing errors and hence facilitate the whole commissioning phase of the project.

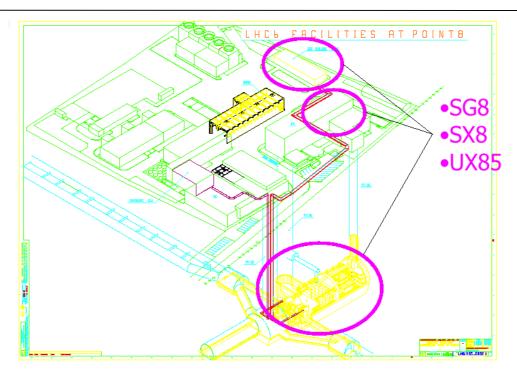

The sub-detectors will be located in the US8 cavern of the LHC accelerator and will be inaccessible during data taking. This imposes stringent constraints on the components of the control system that are located at or near the detector and are therefore exposed to radiation. To guarantee continuous control over the electronics in the cavern, the interfaces to the control system have to be immune to radiation effects, especially Single Event Upsets (SEUs). If SEUs occur, they must be detected and the control software should be able to recover from them in a transparent way.

# 2.3 LHCb Trigger System

The nature and topology of the events containing B-mesons are such that it is extremely difficult to completely distinguish these events from background events generated by other physics processes, e.g. to discriminate an event containing b-quarks from an event containing c- or s-quarks. Independent sets of trigger algorithms largely based on sophisticated pattern recognition code and working on complete events are required to select each event topology of interest. These algorithms, which constitute the so called high-level triggers, must therefore run on powerful general purpose processors after the event-building stage. Two levels of triggering will therefore be applied at the front-end electronics in order to pre-select an enriched sample of interesting events, such that the data acquisition system can be realised with a reasonable effort in resources. Thus two trigger decisions must be distributed to the front-ends and temporary buffering of the data is needed after each stage for the latency of the triggers. This has implications for the system used to distribute the clock and trigger signals to the front-end electronics (the Timing and Fast Controls (TFC) system), and also on the architecture of the front-end Electronics itself. The latter is described generically in [6] and the specific implementations are outlined in the TDRs of the individual sub-detectors.

The characteristics of these first two trigger levels are described in Table 2 in terms of input/output rates and the detectors whose data are used to reach a decision.

|                     | Level-0                           | Level-1                     |

|---------------------|-----------------------------------|-----------------------------|

| Input Rate          | 40 MHz                            | Level-0 accept<br>(1.0 MHz) |

| Average Accept Rate | 1.0 MHz (max.)                    | 100 kHz (max.)              |

| Detector Data used  | Calorimeter,Muon,<br>Pile-Up Veto | VELO, Level-0               |

| Latency             | 4.0 μs (fixed)                    | <2 ms (variable)            |

Table 2 Characteristics of the first two LHCB trigger levels

The CPU power required to execute the high level algorithms has been estimated from performance measurements made of the pattern recognition and track fitting software used for the reconstruction of simulated events. The Level 2 trigger is designed to match vertex information from the VELO

2 Requirements page 7

with momentum information provided by the tracking system. Most of the CPU requirement comes from the momentum measurement and results in an estimate of 0.25 SI95•s per event. The Level 3 trigger uses refined and optimised reconstruction algorithms to select B decays with different topologies and for this stage the goal is 5 SI95•s per event. This can be compared to the estimate for the full reconstruction which is 250 SI95•s per event. These estimates have been made under the assumption of a significant optimisation of the current software. More accurate estimates are expected once the high level trigger studies have been completed and these will be described in the Computing TDR.

It is expected that the high level trigger software will be adapted and enhanced with time as experience is gained running the experiment. It will therefore be a considerable advantage to have the full event data immediately made available such that full flexibility can be used in developing algorithms that can make use of data from all detectors. This will have implications on the choice of the readout protocols, as will be seen in later chapters.

### 2.4 LHC Accelerator

A dedicated communication protocol will be needed to communicate control and status information between LHCb and the LHC machine. Information from the machine indicating particle intensities and currents, collimator and magnet settings and current activity (e.g. 'injecting', 'stable beams', dumping' etc.) must be interlocked with LHCb operations to ensure that the detector is always in a safe operational state. It will also be necessary to log enough information from the machine in order to be able to determine the machine energy with the best possible accuracy. The LHC machine will also provide the master clock corresponding to the bunch crossing rate (40.08 MHz) and this must be distributed to the front-end electronics and trigger system via a low-jitter timing distribution system.

Conversely, LHCb will provide the LHC machine with relevant information about the LHCb experiment, such as the status of the magnet, estimates of the background conditions in our detector and measurement of the luminosity. There might be a need to prevent the LHC machine from continuing its current activity, should the radiation conditions in the LHCb detector become unacceptable. This implies a fast feedback and interlock mechanism between the LHCb experiment and the LHC machine. This mechanism and its triggering is outside the scope of this TDR. It should however be possible to trigger the appropriate action from the ECS system as well.

The mechanisms through which information is exchanged between experiment and machine should be standardized and flexible such that new information can be added when required. It is not expected that the information is updated very frequently, i.e. on a time scale of seconds. This issue is being addressed in common between the 4 LHC experiments and the LHC machine in a joint working group<sup>2</sup>.

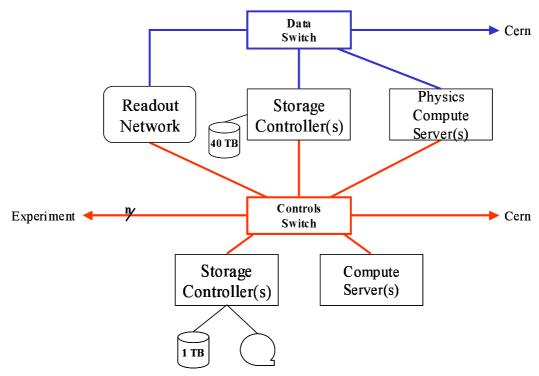

# 2.5 Data Processing and Offline Computing

The DAQ system is responsible for formatting data such that their origin can be understood and their integrity verified. In a continuous mode of running, it is practical to reconstruct events promptly as the data are collected. This will give immediate feedback to the shift crew on detector performance and immediate access to the physics. This requires that a accurate calibration and alignment of the detector can be achieved in real-time and that the appropriate parameters can be made available to the reconstruction program.

Page 8 2 Requirements

<sup>&</sup>lt;sup>2</sup> Data Interchange Working Group.

The offline software will also require information on the settings of the trigger, and of the detector support systems (high and low voltage, gas compositions and pressures, operating currents etc.). These data vary with time and therefore this information will have to be recorded in such a way that it can be time-correlated with the corresponding event data. A data repository (Conditions Database) targeted towards accessing contents by time interval will be required to store this information, together with calibration and alignment data, such that 'conditions' information corresponding to the event being processed can be rapidly located. The performance of the software in retrieving information should scale well as the size of the database increases. This repository will need to be replicated in remote computing centres wherever LHCb data are processed and analysed.

Re-processing of the data must be envisaged to take account of changes in the alignment as well as in the software used to reconstruct the events. It is also foreseen that the online CPU facility, which normally executes the high-level trigger algorithms and prompt reconstruction on the event data, will be used during shutdown periods as a computing infrastructure for re-processing (re-reconstruction) of the event data taken during the previous data-taking periods. This means that complete access to the conditions database has to be provided for this running mode.

The physics data will need to be stored on permanent media for a long time and have to be accessible any time from any institute in the collaboration. A natural place to effect the storage is the CERN computer centre. Hence, we will buffer the raw data and the output of the reconstruction temporarily within the online system and send them immediately through links to the computer centre (i.e. making use of the central data recording facility) where they will be stored permanently on magnetic tape.

# 2.6 Experiment Operations

It should be possible to operate the experiment with a small number, -two should be enough-, of people present in the control room. This implies that control and operation of all aspects of the online system must be accessible from a central console under the command of the shift leader. The main console should therefore have access to the control of all sub-detector support systems (e.g. high voltage) and to the charts and histograms that are used to monitor the integrity of the data coming from all the apparatus.

Many members of the shift crews will be non-experts of the online system. To obtain maximum efficiency of the experiment as many as possible of the routine procedures should be automated, such as starting data taking, raising and lowering the high-voltages of the detector or recovery from errors.

Remote operation of the experiment or parts of it must be possible to allow experts to exercise control over the equipment to fix problems or improve the performance. This implies that the control system has to be distributed and network-based.

# 2.7 Running Modes and Partitioning

Partitioning is an important concept denoting the possibility to sub-divide the LHCb online system into smaller functional parts that can be operated independently and concurrently. This notion has significant implications on the design of the system, specifically on all aspects of controls (Fast Controls and Experiment Controls), since it is the ability to control the partitions independently that will allow this requirement to be fulfilled. In the data-flow sub-system, partitioning has to be taken into account at the level of the layout and assignment of components to possible partitions as not to break the operational independence. For example, if a readout module were shared between two

2 Requirements page 9

sub-detectors, it would be impossible to initialise the module by one sub-detector, since it would disrupt data taking by the other. Hence, e.g. Readout modules have to be associated to sub-detectors (at least).

Partitioning will show its power when being used for operating different sub-detectors under different running conditions. A multitude of running modes can be envisaged [7], such as

- Normal physics data taking

- Pedestal and electronic gain calibrations

- Timing calibrations

- Alignment calibration

- Test and debugging activities

The system has to be designed for optimal physics running. However, nothing in the system should prevent the other activities, even if they are given lower priority and run with lower efficiency.

### 2.8 Infrastructure Services

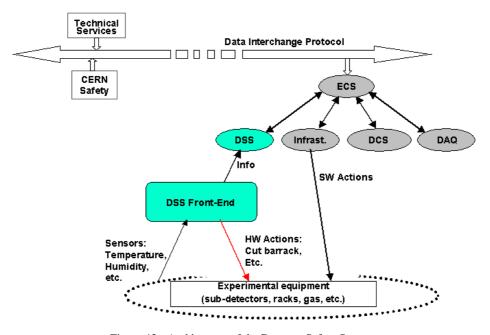

As with the LHC machine there will also exist an information interchange between the LHCb experiment and CERN's infrastructure services: the technical service and the safety service. This information flow will be mostly unidirectional and will comprise items such as:

- The state of the power distribution system

- The state of the cooling and ventilation system

- Information about safety warnings and alarms at or around the LHCb experimental area

- The lists of personnel accessing the LHCb pit

- This information, together with information on environmental parameters (such as: temperature, humidity, radiation levels, etc.) gathered by the experiment itself will be used in order to keep the operators informed and also to protect the sub-detectors and associated equipment from undesired conditions.

- There will be three safety levels in LHCb:

- The first level is performed by software, it will be based on correlations using the above mentioned information. It can perform actions in an organized and orderly manner. For example, if a temperature in a rack rises above a certain limit it would switch off the crates in this rack one by one and then the rack itself. This task will be performed by the LHCb experiment control system.

- The second level is hardwired, it will be based on sensors installed by LHCb in well chosen locations and simple logic decisions leading to crude actions. For example if a temperature raises above a certain level (higher than the software threshold) the power to the entire counting room would be cut. This task is the responsibility of LHCb's Detector Safety System (DSS).

- o The third level is also hardwired, it will be activated for problems leading to personnel danger and would take even stronger actions, such as cutting the power to the experimental area. This is the responsibility of the CERN Safety System.

Page 10 2 Requirements

# 2.9 Summary of performance requirements

The LHCb DAQ system is designed against the parameters compiled in Table 3. These parameters have been deliberately set to be conservative and are current estimates only. The system will be adapted to new sets when they become available in the course of time.

Table 3 Design parameters for the initial LHCb DAQ system

| Parameter                                    | Value              |

|----------------------------------------------|--------------------|

| Average Physics Event-Size <sup>+</sup>      | 100 kB             |

| Average Level-1 Trigger rate                 | 40 kHz             |

| Average Total Data Rate                      | 4 GB/s             |

| CPU power for Level-2 Algorithm              | 0.025 SI95·s/event |

| Total CPU power needed for Level-2 algorithm | 10000 SI95         |

| Average Level-2 Accept Rate                  | 5 kHz              |

| CPU Power needed for Level-3 Algorithm       | 5 SI95·s/event     |

| Total CPU power needed for Level-3 algorithm | 25000 SI95         |

| Average Level-3 Trigger Rate                 | 200 Hz             |

| CPU Power needed for Reconstruction          | 250 SI95·s/event   |

| Total CPU power needed for Reconstruction    | 50000 SI95         |

| Average Event Size to Storage (RAW/ESD data) | 200 kB             |

| Average data rate to Storage                 | 40 MB/s            |

<sup>&</sup>lt;sup>+</sup> Larger events, up to ~5 MB, must be accepted, albeit at a reduced readout rate.

2 Requirements page 11

# 3. System Design

This chapter will outline the design of the LHCb online system. Starting from an architectural design we will describe all the individual components in detail. The design is of course subject to certain constraints and limitations, being primarily resources (financial and manpower) but also technological. In the following we first state some of the design goals, describe the overall architecture and give functional details on each component of the system

# 3.1 Design Goals

The basic design principle of the online system is simplicity, within the boundary condition that all the requirements must be fulfilled. The reason for this is that, given the expected scale of the system in number of modules and links, only by simple functionalities of the individual components and simple protocols can a reliable operation of the system be expected. Within budgetary possibilities, we also accept higher performance requirements for certain components of the system (e.g. the event-building network), to follow this design principle.

Another design goal we follow strictly is the separation of the control and data paths. From experience at the LEP experiments, this separation is extremely important for a reliable operation and efficient diagnostics in case of failures. Again, this principle can lead to slightly higher cost, but this will be compensated by higher reliability and robustness of the system.

We also adhere to the largest extent possible to the goal of avoiding shared buses across boundaries of modules. All links between modules are to be point-to-point links. While this is necessary for performance reasons at the downstream levels of the dataflow system, for homogeneity reasons we adhere to this also in the upstream regions. Again, we believe, this will increase the diagnostics capabilities and hence the overall efficiency of the system.

Homogeneity is another design goal we follow. We will try to re-use modules and functionalities wherever we can, specifically for maintenance and operations reasons, but not least also for cost reasons, since we can increase the number of a type of module and hence decrease its cost. Within availability we try to use industrial equipment and adhere to standards where existing. For cost reasons, wherever possible, we use mainstream technologies, such as Gigabit Ethernet.

Last, but not least, scalability, i.e. the possibility to extend the range of operating parameters (event size or trigger rate) without changing the architecture or the protocols, was also a major design criterion. This is important since the real running conditions will not be known until after the start-up of the experiment.

As will be seen in later chapters of this document, we have put a lot of emphasis on simulating architectures and protocols at different levels, such as the TFC components, the Readout Units and the Readout Network. The results of these simulations gave important feedback for the final design of the system.

# 3.2 System Architecture

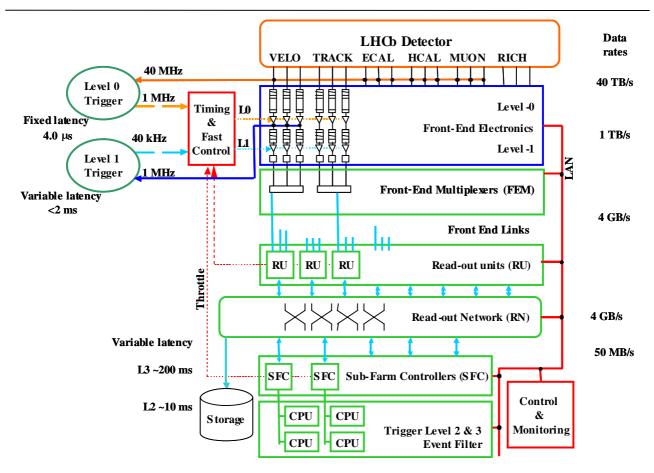

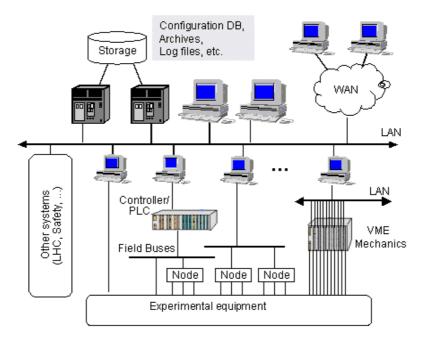

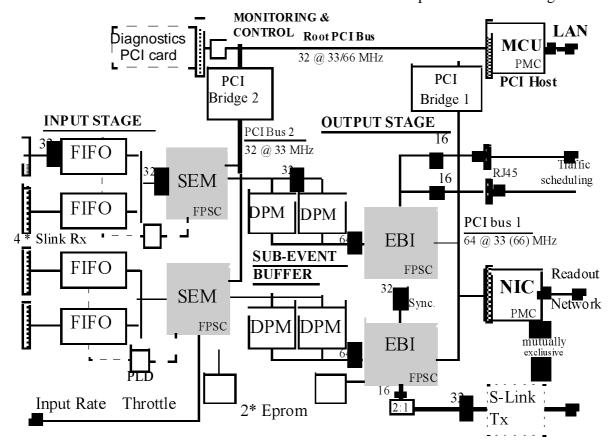

The overall architecture of the dataflow system is depicted in Figure 4.

Page 12 3 System Design

Figure 4 Overall architecture of the LHCb online system. All rates mentioned are expected maximum averages.

The main components of the system are as follows:

- The Timing and Fast Control system, which is used to distribute the clock, the decisions of the Level-0 and Level-1 trigger system and other synchronous commands to the front-end electronics

- A data-flow sub-system that collects data from the front-end electronics and transfers them to a CPU farm for execution of the software trigger algorithms. The data-flow system itself is composed of the following elements

- o A multiplexing stage which reduces the number of links from the front-end electronics into the event-building network by aggregating the data

- o A 'Readout Unit' layer acting as multiplexer and gateway between the front-end links and the readout network

- The Readout Network, routing event fragments belonging to the same event from its inputs to a single destination

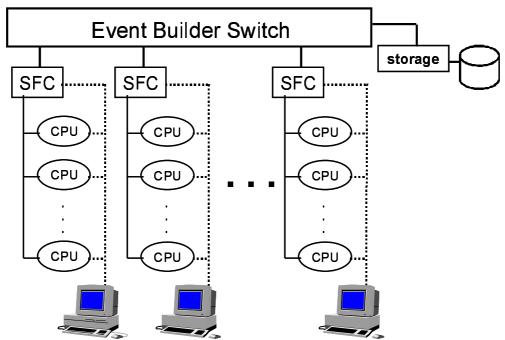

- A layer of sub-farm controllers performing the final event-building and acting as an interface and insulation layer between the Readout Network and the individual CPUs of the farm

- A CPU farm, providing the hardware infrastructure for high-level filter algorithms and reconstruction of accepted events

- Temporary storage for physics data and general computing infrastructure for the online system

- The control and monitoring system, which is used to configure all components for data taking and to monitor their operational state. This constitutes the control path.

# 3.3 Timing and Fast Controls

The Timing and Fast Control (TFC) [6] system control the distribution of timing, trigger, and synchronous control information to the front-end electronics. A special feature of LHCb is that the system has to transmit two levels of high rate triggers. This information has to arrive synchronously at all the front-end electronics. The system must provide for means to achieve timing alignment of the front-end electronics and introduce minimum jitter. The system must incorporate functionality to prevent buffer overflows in the entire readout chain, and provide means of different types of auto-triggering for tests and calibrations. The TFC system must also support readout partitioning [9] in order to be able to run small sub-systems independently in special running modes. The system should provide statistics on the performance of the synchronous readout.

More specifically the information to be distributed includes the following:

- LHC reference clock at ~40 MHz as received from the LHC timing generators via the LHC machine interface (TTCmi). This clock drives all the electronics in the synchronous readout.

- L0 and L1 trigger decisions.

- Commands resetting event related counters in the front-end electronics used to identify the accepted events and to check synchronisation.

- Commands resetting the front-end electronics in order to prepare it for data taking or to recover from an error condition.

- Calibration commands activating specific calibration systems in the front-end electronics or

in the sub-detectors. The TFC system must have a mechanism to guarantee that triggers

corresponding to calibration events are accepted.

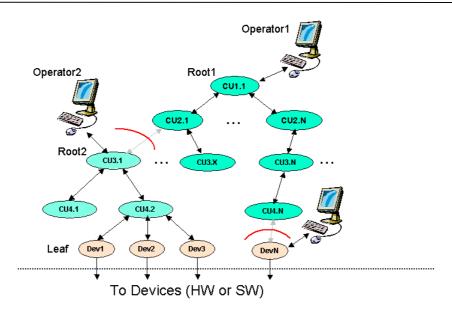

### 3.3.1. TFC Architecture and Partitioning

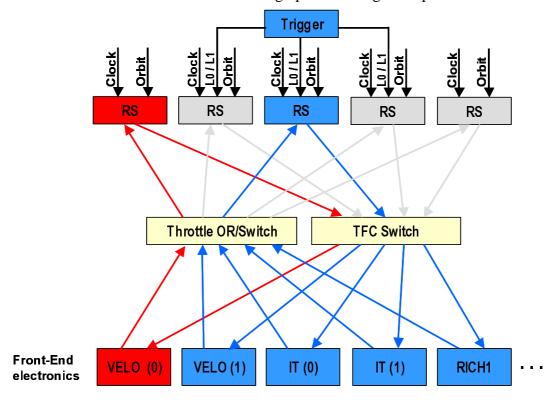

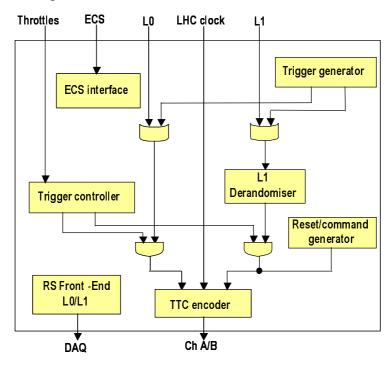

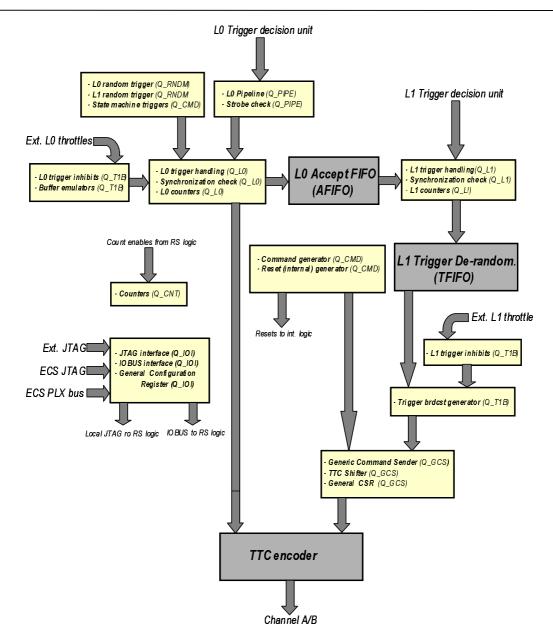

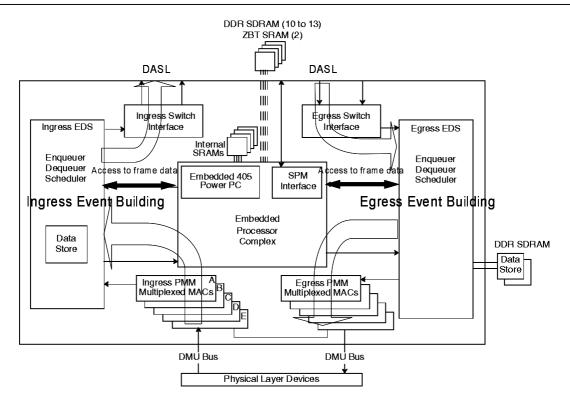

Figure 5 shows a logical picture of the TFC architecture. In order to simplify the implementation of a partitionable system, the entire mastership of the Timing and the Fast Control has been implemented in one type of module: the Readout Supervisor. It receives the LHC bunch clock and the orbit signal from the LHC machine interface (TTCmi) [2], and the L0 and the L1 triggers from the trigger Decision Units, and has the crucial task of providing the functionality listed above.

Buffer overflows are prevented by monitoring the occupancy of the buffers in two different ways. The occupancy of the L0 derandomisers and the L1 buffers in the front-end electronics are emulated centrally by the Readout Supervisor. Buffers further down the readout chain monitor their occupancy locally and, in case the buffers get nearly full, signal the Readout Supervisor via a hardwired signal. Overflow is prevented in the Readout Supervisor by throttling the triggers, i.e. converting trigger accepts to trigger rejects until the occupancy is reduced.

As a consequence of its primary role, the Readout Supervisor must firstly be highly reliable. In addition, it must also be versatile in order to support many different types of running modes, such as tests, debugging, various types of calibrations, physics data taking etc.

As shown in Figure 5, the system architecture incorporates a pool of Readout Supervisors, one of which is reserved for normal data taking. The other Readout Supervisors are reserves that can be invoked for tests, calibrations and debugging. The reserve Readout Supervisors also allow connecting local trigger units.

The TFC Switch [11] realises the partitioning of the TFC system. It is a programmable patch panel that allows distributing the synchronous information to different parts of the front-end electronics. It can be programmed to distribute the information from one Readout Supervisor to one part of the front-end electronics and simultaneously distribute information from another Readout Supervisor to

Page 14 3 System Design

a second part of the front-end electronics. The two Readout Supervisors can be configured to sustain completely different timing, triggering, and control. The two sub-systems are independent and define two different partitions. In the example in Figure 5, the leftmost Readout Supervisor control half of the VELO sub-detector in a stand-alone test, while the Readout Supervisor in the centre control all the other sub-detectors for physics data taking. The three other Readout Supervisors are idle and can be reserved for setting up and driving other partitions.

Figure 5 The TFC architecture simplified to show an example of partitioning.

The Throttle Switch [11] feeds back the throttle signals to the appropriate Readout Supervisors from the L1 trigger system, the L1 de-randomisers in the front-end electronics and components in the data-driven part of the DAQ system in case of imminent buffer overflows.

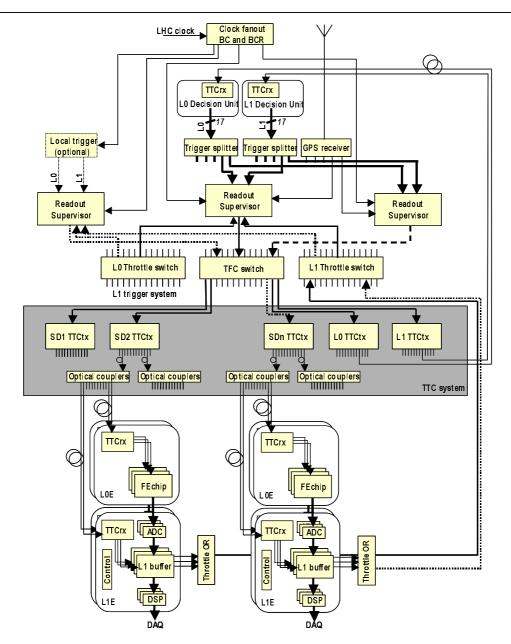

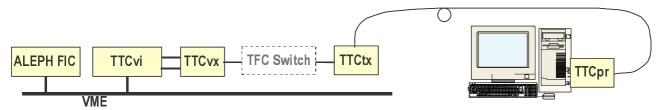

Figure 6 shows the TFC architecture in detail. Several Readout Supervisors are connected to the trigger decision units to be able to run stand-alone tests with physics triggers. There is one Throttle Switch for throttle signals that throttle the L0 trigger, and one Throttle Switch for throttle signals that throttle the L1 trigger. The TFC distribution network is based on the RD12 Trigger, Timing, and Control (TTC) system [2] used by all four LHC experiments. The TTC system distributes the timing, trigger, and control information optically on two serial channels. Channel A is a low-latency channel that allows transmitting a one-bit trigger signal at 40 MHz. Channel B can transmit two different types of broadcasts, which includes six or 16 bits of user defined information. The LHCb TFC system utilises the TTCtx for the conversion of the TTC signal from electrical to optical. TTC receiver chips (TTCrx) incorporated in the front-end electronics receive the TTC signals and decode the channel A and the channel B information.

The Throttle ORs [11] form a logical OR of the throttle signals from sets of front-end electronics and readout components further down the readout chain.

A GPS system allows time stamping status information sampled in the Readout Supervisor.

Figure 6 Overview of the TFC system architecture.

#### 3.3.2. TTC Distribution System

LHCb is different from the other LHC experiments as it has to transmit two levels of high rate triggers to the front-end electronics: the L0 trigger at 40 MHz and the L1 trigger at a maximum of ~1.1 MHz<sup>3</sup>. Nevertheless, the functionality of the TTC system has been found to suite well the LHCb application. The LHC reference clock is transmitted to the front-end electronics using the TTC bi-phase signal. Channel A is used to transmit the LHCb L0 trigger decisions to the FE electronics in the form of an accept/reject signal at 40 MHz.

Channel B is used for several functions:

• Transmission of the commands to reset the Bunch Counters (BCR) and the Event Counters (ECR) in the front-end electronics and the trigger systems. The Bunch Counter counts

Page 16 3 System Design

<sup>&</sup>lt;sup>3</sup> The nominal Level-1 decision rate is 1 MHz. The maximum Level-0 accept rate is 1.1 MHz and is a consequence of the specification to the Level-0 electronics that one event has to be processed within a maximum of 900 ns [10]

bunch-crossings, and the Event Counter counts the number of accepted L0 triggers, which in LHCb is referred to as the L0 Event ID.

- Transmission of the L1 trigger decision.

- Transmission of front-end control commands, e.g. electronics resets, calibration pulse triggering etc.

The information is transmitted in the form of the short TTC broadcast format. The short broadcasts contain six bits of user-defined information and two bits that have been reserved in the TTC system to reset the L0 Event ID (Event Counter) and the Bunch Counter. The different commands listed above are encoded in the six user-bits.

In principle, the TTC channel B bandwidth would allow up to a rate of 2.5 MHz of short broadcasts. However, since this is a unique use of channel B that was not foreseen initially and it is crucial to LHCb, this has been a critical test to perform.

The TTC receiver chip also provides means to adjust the timing of the TTC information in order to time align all front-end electronics.

### 3.3.3. Readout Supervisor

The Readout Supervisor (RS) has the crucial task of controlling the synchronous readout of LHCb. Therefore it must be designed with emphasis firstly on reliability. Secondly, it must be versatile in order to control the readout in the most efficient way and support a wide spectrum of running modes for tests, debugging, and calibration. It may also be necessary to change or add functions in order to handle changes, upgrades, or even unforeseen problems. Therefore, a design criterion has also been modifiability. Below is a short summary of the readout Supervisor functions. A complete description can be found in [12].

The Readout Supervisor receives the L0 and the L1 trigger decision from the L0 trigger Decision Unit (L0DU) and the L1 trigger Decision Unit (L1DU), respectively. In order to verify that the decision units are synchronised, event identifiers accompany the trigger decisions.

The Readout Supervisor also provides several means for auto-triggering to be used in conjunction with tests and calibration runs: random trigger, periodic trigger, triggering at a programmable time after sending a command to fire a calibration pulse etc.

If the physics trigger rate gets abnormally high or data congestion occurs in the system, there is a potential risk of overflow in the buffers in the front-end electronics and in the DAQ system. In order to prevent this, the Readout Supervisor controls the trigger rates according to the status of the buffers. The statuses of the buffers are either emulated centrally in the Readout Supervisor or they are monitored locally. In case they are monitored locally, imminent overflows are signalled via the dedicated throttle wires. Data congestion at the level of the L2/L3 farm is signalled via the Experiment Control System (ECS) to the Readout Supervisor.

The Readout Supervisor also has the task of transmitting various synchronous reset commands in order to prepare the front-end electronics for data taking or recover from an error condition.

The Readout Supervisor provides statistics on the performance and the efficiency of the synchronous readout (dead-time, errors, etc) and records local event information that is appended to the event data.

The clock, the L0 and the L1 triggers, and all the control commands are encoded and transmitted by the Readout Supervisor to the front-end electronics as a TTC signal.

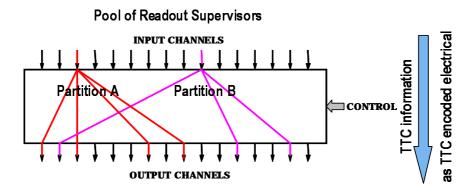

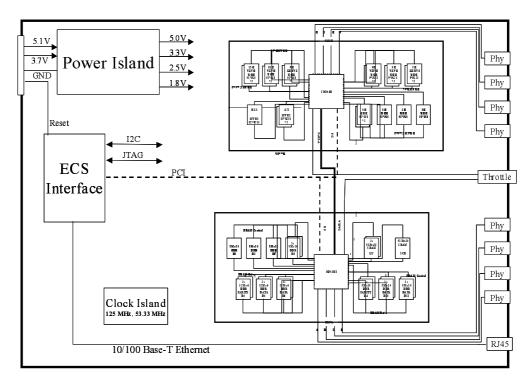

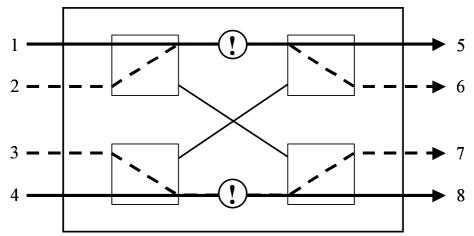

#### 3.3.4. TFC Switch

As shown in Figure 7, the TFC Switch allows setting up a partition by associating a number of partition elements (e.g. sub-detectors) to a specific Readout Supervisor. The Readout Supervisor can then be configured to control and trigger the partition in whatever specific mode that is required. Note that the TFC Switch is located before the TTC optical transmitters (TTCtx) and that it is handling the encoded TTC signals electrically.

Front-Ends grouped by TTCtx/Optical couplers to partition elements

Figure 7 The principle of the TFC Switch.

From the architecture of the TFC system it follows that the front-end electronics that is fed by the same output of the TFC Switch is receiving the same timing, trigger, and control information. That is, a part of the Front-End electronics connected to a TFC Switch output cannot be operated in different running mode than another part belonging to the same output. Hence, the association of the front-end electronics to the different outputs of the TFC Switch defines the boundaries between the smallest sub-systems that can be operated independently.

The TFC Switch has been designed as a 16x16 switch and thus allows the LHCb detector to be divided into 16 sub-systems. To increase the partition granularity an option exists whereby four TFC Switches are deployed in order to divide the LHCb detector into 32 sub-systems.

The TFC Switch is subject to two important design criteria. Since the front-end electronics are susceptible to jitter on the TTC signal, the TFC Switch must introduce less than 50 ps of jitter. Secondly, the front-end electronics should be time aligned in order to sample the detector signal at the optimal point. However, different Readout Supervisors may be used to operate the front-end electronics at different times, which in reality means that the TFC signals take different paths in the TFC Switch. Since the front-end electronics is susceptible to the timing, it is crucial that the propagation delays of all paths in the TFC Switch are equalised. The aim is that the phase difference between output ports using any input should be less than 100 ps.

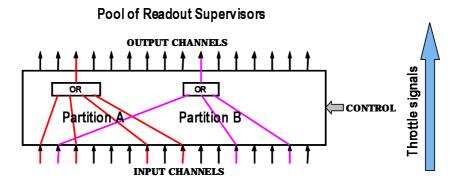

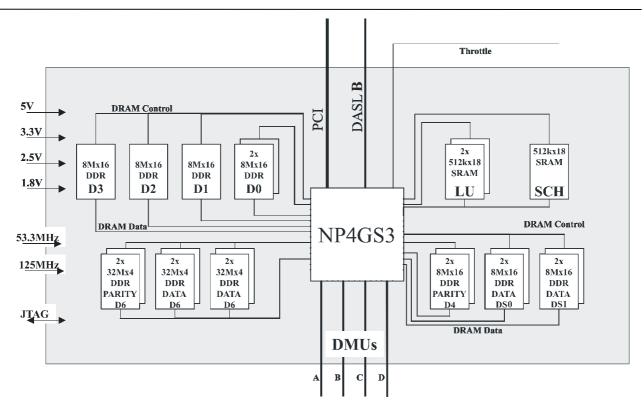

#### 3.3.5. Throttle Switch and the Throttle OR

The function of the Throttle Switches is to feed back the throttle information to the appropriate Readout Supervisor, such that only the Readout Supervisor in control of a partition is throttled by the components within that partition. Figure 8 shows an example of how they are associated. The logical operation of the Throttle Switch is to perform a logical OR of the inputs from the components belonging to the same partition. The system incorporates two Throttle Switches, a L0 and a L1 Throttle Switch. The sources of L0 throttles are essentially the components that feed the

Page 18 3 System Design

L1 trigger system. The sources of L1 throttles are the L1 de-randomisers and the event-building components.

Front-Ends etc grouped by Throttle ORs i.e. ~Throttle Switches

Figure 8 The principle of the Throttle Switches.

The Throttle ORs group throttle lines belonging to the same partition elements. They are identical to the Throttle Switches in all aspects except that they OR 32 inputs and have only one output.

# 3.4 Dataflow System

As mentioned in section 3.2 the data-flow system is composed of four distinct components. These are responsible for transporting the data from the Level-1 front-end electronics to permanent storage. In the following sections, we will describe the functionalities of these component in detail.

### 3.4.1. Front-End Multiplexer Layer

The purpose of the Front-End Multiplexer (FEM) is to aggregate the data fragments originating from several Level-1 front-end Electronics boards, which have very low data rates into bigger fragments with the final aim of reducing the number of links into the readout network and making better use of the single link bandwidth. For example: The VELO detector is expected to deliver 3.3 MB/s from each Level-1 front-end electronics board (cf. Table 7). It would be highly inefficient and costly to feed each of the 100 VELO-links into the readout network. Therefore it is advantageous to aggregate ~25 of those links onto one input of the readout network. On the other hand, for example the SPD/PS detector will feed 39 MB/s on one link into the DAQ system. There is clearly not too much room for aggregation in this area. Hence, a flexible data aggregation scheme is needed.

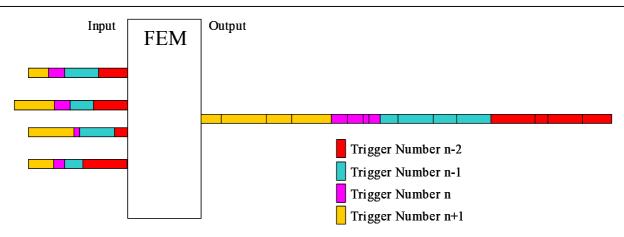

The aggregation is done by combining the data belonging to the same event-number and arriving on different input links, after having removed the transport headers and trailers. The resulting data are framed again with transport information and sent out on the output link to the next higher stage in the readout. Figure 9 shows graphically the event-building process in the FEM modules. The data fragments of n input streams (in Figure 9 n is equal to 4) are merged according to event number to one output stream, while the original event-building information contained in the headers is removed and substituted by a single new header reflecting the characteristics of the newly created data fragment.

Figure 9 Pictorial view of the data aggregation or event-building process

### 3.4.2. Readout Unit Layer

The Readout Unit (RU) collects data from several input links, concatenates and buffers them and finally sends them to a Subfarm controller. The functionality of the readout units (RU) is in the first instance the same as that for the FEMs (Multiplexing/Data Merging, see Figure 9). In addition, the RUs are connected to the readout network. The readout network can, for certain technologies, suspend the sending of data to it, and hence block the RUs. This can lead to congestion in the RUs, which in turn entails significant buffering requirements for the RUs.

The RU must adapt the protocol used on the input links to that of the Readout Network. The extent of this translation will be depending on the choices for the input link technology and the technology for the readout Network. In the terms of network language, they act as a gateway between the two technologies.

A third feature required of the RUs has to do with the event-building process. Unlike the FEMs, the RUs can send their data to more than one destination through the Readout Network. The fragments of a given event-number must arrive at only one destination. Hence, the RUs have to support a destination assignment mechanism (see 3.4.5).

#### 3.4.3. Readout Network Layer

There are two main functional requirements imposed on the Readout Network:

- Provide the connectivity between the RUs and the Sub-farm Controllers such that each RU can communicate to any Sub-Farm Controller,

- Provide the necessary bandwidth, such that all data arriving in the RUs can be sent to the Sub-Farm Controllers. The aggregate data bandwidth is ~4GB/s (100 kB events at 40 kHz).

The operation of sending all data fragments belonging to a particular event, from each RU to the assigned SFC is called *event-building*. At first sight, this data traffic would require N data paths for each end point, or  $N^2$  data links between N RUs and N SFCs. However most of those links would be active only during 1/N of the time.

The connectivity requirement (point 1) can, in principle, be fulfilled by a 'non-blocking' switching network such as those used by the telecom industry or for the interconnection of processors. The property of being non-blocking means that data transfers can take place in parallel between sources and destinations, for any combination where one source at most is connected to a destination at a

Page 20 3 System Design

<sup>&</sup>lt;sup>4</sup> A temporary congestion of 10 ms would lead to the accumulation of 400 event fragments in the RU, which corresponds to a buffering requirement of the order of 800 kB.

given time. This property could be used for event-building if a global control system could change, at regular time intervals, the non-blocking interconnection pattern of the RUs and the SFCs so that after N such patterns any RU has been connected once to every SFC. This traffic-shaping scheme is called a *barrel shifter*. However we wish to avoid such a complication that implies the use of a global control system over the Readout Network.

We show in chapter 4 that event-building over a "packet switching" network is doable even if the RUs send their event fragment to the assigned SFC, without caring about possible contention in the network. In fact packet switches provide internal buffering to resolve contention. We still have to prove that the event-building traffic, as it is specified, will not overflow those buffers, with a probability such that condition 2) can be fulfilled. It will be shown that this is possible at the condition that the overall load on the network is significantly less than 100%, in other words that the installed bandwidth exceeds the value of 4GB/s mentioned above.

For the selected technology, Gigabit Ethernet, a bandwidth of approximately 6 GB/s would be sufficient to sustain the "normal" traffic with a low probability of data loss. It is important to ascertain this since the throttle mechanism is, in principle, unable to avoid data losses due to buffer overflow inside of the Readout Network. Consequently, the Readout Network should be implemented in such a way that the throttle mechanism only comes into action when an excessive data flow persists.

An additional requirement is that the readout network must be able to accept occasionally very large events carrying calibration data. Precise specifications for such events are not available presently. Such large events may possibly to cause buffer overflows and will require special attention.

To ensure scalability of the system, our choice is to avoid the use of a central event manager for assigning dynamically a destination SFC for each event. This function will be implemented as a fixed round robin destination assignment. The implications of this choice are briefly discussed in section 3.4.5.

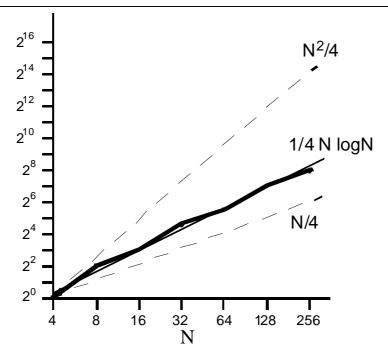

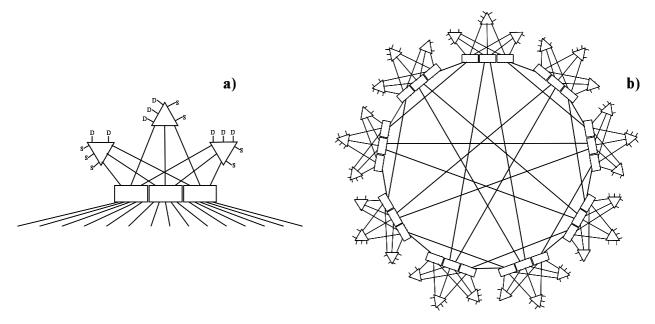

A possible upgrade to higher data throughput, due to larger events and/or to a higher trigger rate, beyond the safe limits of the implemented system, will necessitate a redistribution of the front-end data and an increase of the number (N) of input and output ports of the Readout Network. The size of the network, in terms of number of components (switching modules, internal links) scales roughly like NlogN, as illustrated in Figure 10 which shows the number of switching modules required to build an NxN switching network based on 4x4 switches inter-connected in a Banyan topology [13]

Figure 10 Number of 4x4 modules required to build an NxN switching network (Banyan topology)

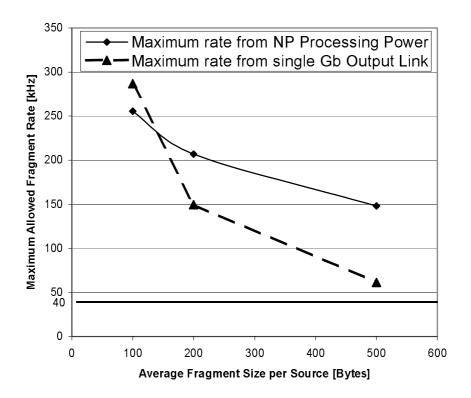

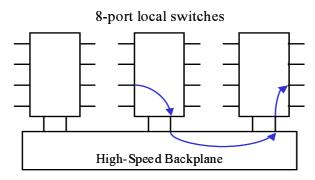

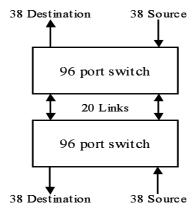

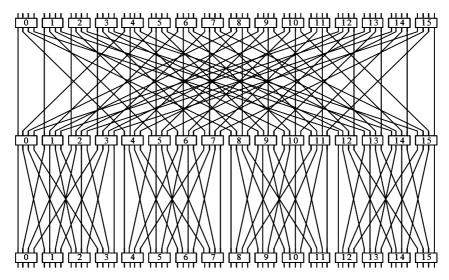

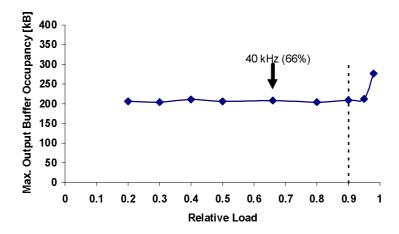

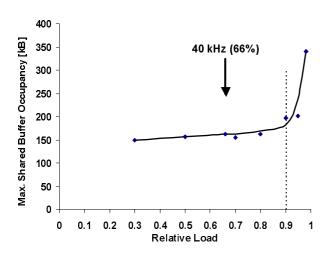

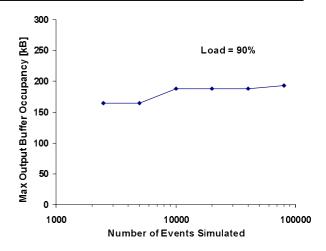

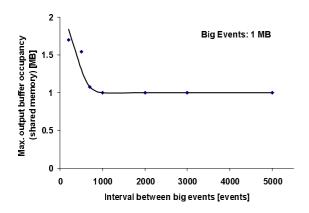

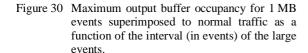

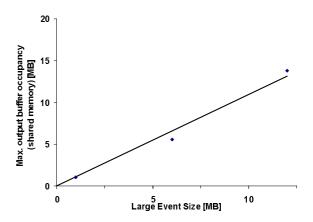

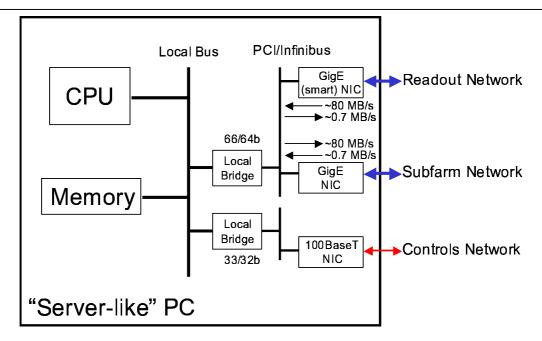

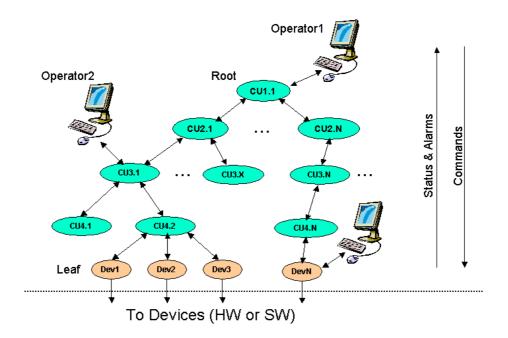

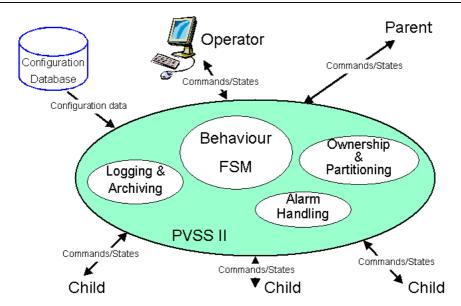

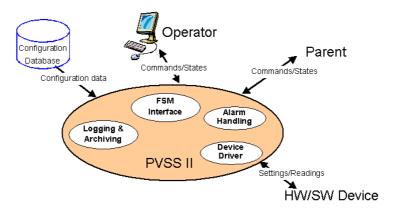

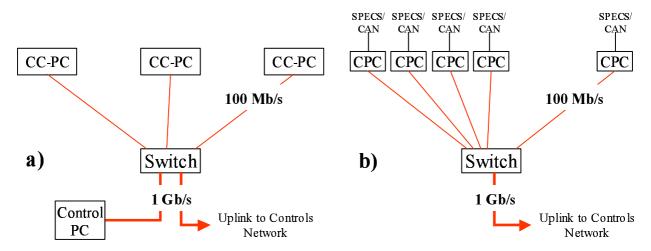

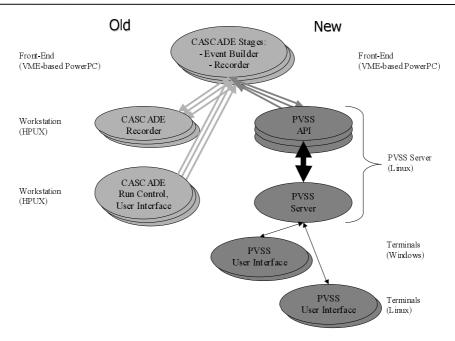

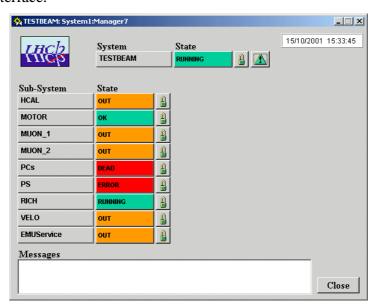

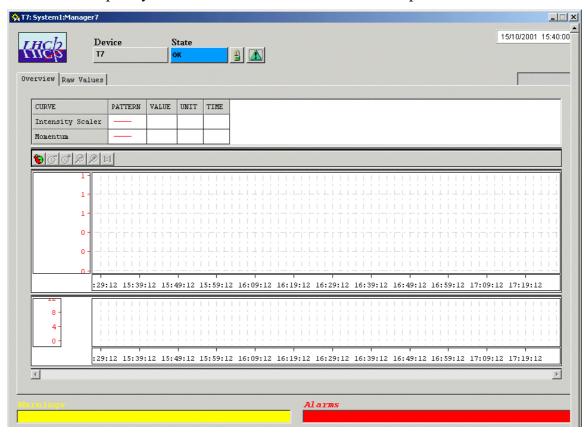

### 3.4.4. Sub-Farm Controller Layer